CPLD explicou: um guia para dispositivos lógicos programáveis

No mundo dinâmico do design eletrônico, os dispositivos lógicos programáveis complexos (CPLDs) se destacam como ferramentas versáteis, misturando perfeitamente adaptabilidade, precisão e eficiência.Esses dispositivos revolucionaram o design do circuito, introduzindo células macro programáveis e uma matriz de interconexão dominante, permitindo a criação de funções lógicas complexas com confiabilidade notável.Desde o início na década de 1980 até o papel principal de indústrias modernas, como redes, automotivas e aeroespaciais, as CPLDs provaram que você busca a flexibilidade e o desempenho.Este artigo se aproxima da jornada de CPLDs, seus recursos distintos, aplicações práticas e as metodologias de programação que os tornam uma pedra angular no design da lógica digital.Catálogo

Visão geral do CPLD

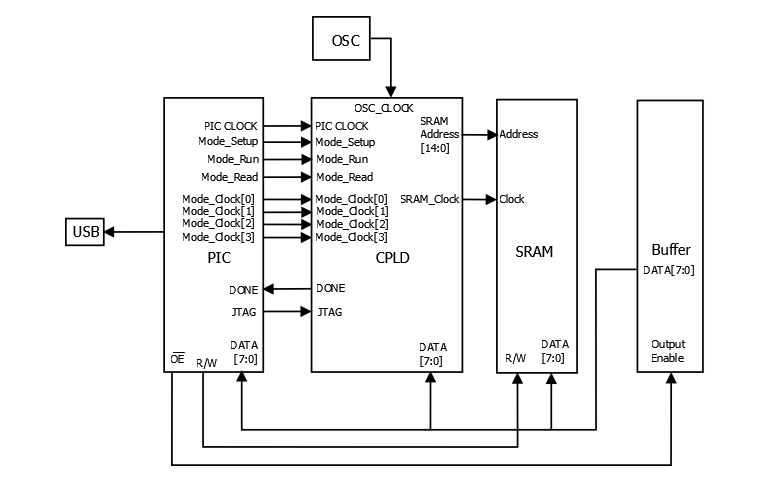

Dentro do domínio de dispositivos lógicos programáveis complexos (CPLDs), descobre uma tapeçaria sofisticada de células macro programáveis lógicas, entrelaçadas através de uma matriz de interconexão dominante.Essas linhas de unidade macro célula (MC) e entrada/saída (E/S) permitem projetar habilmente circuitos, configurando as estruturas para funções exclusivas.Ao contrário dos dispositivos perplexos pelo seu intrincado tempo de interconexão, as CPLDs utilizam fios metálicos imóveis.Essa característica concede a eles um comportamento de relógio consistente e previsível, tornando as previsões de tempo mais confiáveis e precisas.

A jornada e a utilização

A década de 1970 anunciou o advento de dispositivos lógicos programáveis (PLDs), promovendo um movimento em direção a unidades macro programáveis.Essa mudança introduziu ampla flexibilidade de design, diferenciando -os dos circuitos digitais estáticos, embora sua utilidade tenha sido inicialmente restrita a circuitos mais simples.O advento dos CPLDs em meados da década de 1980 revolucionou essa paisagem, abrindo caminho para projetos complexos de circuitos.Desde então, eles se envolvem no tecido de indústrias como redes, eletrônicos automotivos, usinagem CNC e sistemas aeroespaciais.Você pode relembrar a maneira como os CPLDs simplificaram os processos que antes exigiam trabalho manual meticuloso, marcando um salto notável em eficiência.

Qualidades distintas de CPLDs

Os CPLDs se distinguem por meio de sua programação adaptável, integração extensa, recursos de desenvolvimento rápido e aplicabilidade abrangente, juntamente com os custos econômicos de produção.Eles atraem aqueles com experiência mínima de hardware, servindo produtos confiáveis e seguros que não precisam de testes exaustivos.Como testemunho de suas proezas em projetos de circuitos em larga escala, os CPLDs desempenham um papel fundamental no desenvolvimento de protótipos e servem corridas abaixo de 10.000 unidades, incorporando uma competência útil para você.A adepção com a qual as CPLDs se ajustam às demandas em evolução do projeto geralmente lhes agradecem, enfatizando sua versatilidade real em ambientes dinâmicos.

Métodos de aplicação

Esses circuitos integrados permitem que você elabore as funções lógicas adaptadas às suas necessidades, usando os idiomas de descrição de esquemas e hardware nas plataformas de desenvolvimento.Por exemplo, ao projetar uma secretária eletrônica, esquemas e descrições de hardware são preparados e compilados em um computador.Utilizando um cabo de download, o código é transferido para o CPLD para programação no sistema, que compreende testes, solução de problemas e designs aprimorados.Os designs criados com sucesso são produzidos em massa pela replicação dos chips CPLD.Em projetos como os sistemas de semáforo, repetir o processo de design se torna necessário, semelhante a reconstruir uma casa para restaurar sua novidade.Essa metodologia repetitiva geralmente estabelece as bases para dominar, aumentando as habilidades e a confiança.

Variantes principais

Ao longo dos anos, empresas como Altera, Lattice e Xilinx revelaram linhas proeminentes de CPLDs.Exemplos dignos de nota incluem Altera's EPM7128S, Lattice's LC4128Ve Xilinx's XC95108 .Esses modelos encontraram papéis proeminentes em diversas aplicações globais.Aqueles que tiveram o privilégio de trabalhar com esses produtos distintos frequentemente comentam as diferenças sutis, porém poderosas, que otimizam funcionalidades específicas.Isso reflete um bom processo de seleção influenciado por demandas específicas do projeto, onde cada variante mantém seu apelo único.

Identificação e classificação de FPGA e CPLD

|

Aspecto |

CPLD |

FPGA |

|

Formação de comportamento lógico |

Formulário de comportamento lógico usando a estrutura do termo do produto.

Exemplos: Série ISPLSI de Lattice, Xilinx XC9500 Series, Altera Max7000s

Série, série Lattice Mach |

Formulário de comportamento lógico usando um método de pesquisa de tabela.

Exemplos: Xilinx Spartan Series, Altera Flex10k, ACEX1K Series |

|

Adequação |

Adequado para algoritmos e lógica combinacional, funciona

melhor com gatilhos limitados e termos ricos do produto |

Adequado para a lógica seqüencial, funciona melhor com

estruturas ricas em gatilhos |

|

Atraso no tempo |

A estrutura de fiação contínua fornece uniforme e

atrasos previsíveis de tempo |

A estrutura de fiação segmentada leva a um tempo imprevisível

atrasos |

|

Flexibilidade de programação |

Os circuitos internos fixos são modificados para programação.

A programação em nível de bloco lógica é usado |

A fiação interna é modificada para programação.Lógica

A programação no nível do portão permite maior flexibilidade |

|

Integração |

Menor integração em comparação com FPGA |

Maior integração com estrutura de fiação mais complexa e

implementação lógica |

|

Facilidade de uso |

Mais fácil de usar com a programação via E2PROM ou FastFlash.

Nenhum chip de memória externo é necessário |

Requer memória externa para armazenar programação

informações, levando a um uso mais complexo |

|

Velocidade e previsibilidade |

Velocidade mais rápida e melhor previsibilidade de tempo devido a

interconexão agrupada entre blocos lógicos |

Velocidade mais lenta e tempo menos previsível devido a

Programação no nível do portão e interconexão distribuída |

|

Tecnologia de programação |

Usa a programação de memória E2PROM ou Flash.Dados de programação

é retido quando o sistema é desligado.Suporta programação em um

programador ou sistema no sistema |

Com base na programação SRAM.Os dados de programação são perdidos quando

O sistema é desligado e deve ser recarregado.Suporta dinâmico

configuração |

|

Confidencialidade |

Oferece melhor confidencialidade |

Fornece menor confidencialidade |

|

Consumo de energia |

Geralmente maior consumo de energia, especialmente com

maior integração |

Menor consumo de energia em comparação com CPLD |

Linguagens de programação da CPLD

Analisando como os dispositivos lógicos programáveis complexos (CPLDs) são programados é uma pedra angular na criação de soluções versáteis de hardware.Os métodos históricos para a programação de CPLDs confiaram em diagramas de escada ou linguagens de descrição de hardware (HDLs), com o Verilog HDL e o VHDL sendo escolhas predominantes.A linguagem selecionada pode moldar a estratégia de design e a eficiência operacional das implementações.

• Verilog HDL: O Verilog HDL é estimado por seus recursos simples de sintaxe e simulação robusta, refletindo as metodologias usadas no design da lógica digital.Sua integração com as ferramentas de automação de design eletrônico (EDA) permite que você conduza perfeitamente síntese e simulação.Observou-se que a sintaxe do verilog do tipo C diminuiu a barreira à entrada para aqueles com fundos de programação, acelerando a jornada do design para a implantação em uma ampla gama de setores industriais.

• Vhdl: O VHDL fornece uma opção mais elaborada e expressiva para a programação HDL.É frequentemente a escolha de projetos que exigem documentação meticulosa e rigorosa verificação do tipo, características avaliadas nas indústrias aeroespaciais e de defesa.Você pode observar que, apesar da complexidade potencial da VHDL em projetos menores, sua estrutura disciplinada apóia a criação de projetos excepcionalmente confiáveis, uma necessidade em ambientes onde a segurança é dominante.

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

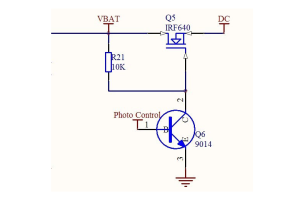

Transistores NMOS: Design, Operação e Aplicações

em 29/12/2024

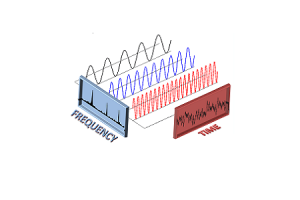

A Fast Fourier Transform (FFT): revolucionando o processamento de sinal digital

em 29/12/2024

Postagens populares

-

Computadores de conjunto de instruções complexos: como eles mudaram de computação?

em 18/04/8000 147765

-

Pinagem e recursos USB-C

em 18/04/2000 111994

-

Usando o Xilinx Unified Simulation Primitives: um guia abrangente para design e simulação do FPGA

em 18/04/1600 111351

-

Tensões de fonte de alimentação em eletrônica: significado de VCC, VDD, VEE, VSS e GND

em 18/04/0400 83753

-

Guia do conector RJ45: pinagem, fiação, tipos de cabos e usos

em 01/01/1970 79548

-

O guia final para os códigos de cores de arame em sistemas elétricos modernos

A maneira como nossos sistemas elétricos usam cores não é apenas para a aparência.Cada cor do fio agora indica uma função específica, facilitando a identificação e manuseio componentes elétricos co...em 01/01/1970 66949

-

Guia da válvula de purga: função, sintomas, teste e substituição para o desempenho ideal do motor

A válvula de purga é uma parte essencial do sistema de um carro que ajuda a manter o ar limpo, gerenciando vapores de combustível antes que eles possam escapar da atmosfera.Isso não apenas ajuda o ...em 01/01/1970 63094

-

Fator de qualidade (Q): equações e aplicações

O fator de qualidade, ou 'q', é importante ao verificar como os indutores e ressonadores trabalham em sistemas eletrônicos que usam frequências de rádio (RF).'Q' mede o quão bem um circuito minimiz...em 01/01/1970 63028

-

Alcançando o desempenho máximo com o teorema máximo de transferência de energia

O teorema da transferência de energia máxima explica como a energia de uma fonte, como uma bateria ou gerador, flui para uma carga conectada.Ele mostra a condição exata em que a carga recebe mais e...em 01/01/1970 54094

-

A23 Especificações da bateria e compatibilidade

A bateria A23 é uma pequena bateria em forma de cilindro com alta tensão.Também chamado 23A, 23AE, ou MN21, funciona a 12 volts e muito mais alto que as baterias AA ou AAA.Seu design espec...em 01/01/1970 52175