EPM7064STC100-7 CPLD: recursos, aplicações e guia de programação no sistema

O EPM7064STC100-7 é um chip poderoso da série Max® 7000S da Intel, projetada para lidar com tarefas complexas em dispositivos eletrônicos.Este guia discute os principais recursos e usos do EPM7064STC100-7, enfatizando sua capacidade de ser reprogramada facilmente, sua operação rápida e seu design flexível.Ideal para muitas tecnologias diferentes, de pequenos aparelhos a grandes máquinas industriais, este chip é uma peça -chave para a construção de circuitos digitais avançados.Catálogo

EPM7064STC100-7 Descrição

O EPM7064STC100-7 é um dispositivo lógico programável complexo (CPLD) da série Max® 7000S da Intel.Possui 64 macrocélulas e 1.250 portões, que ajudam na construção de circuitos digitais complexos.Este chip é executado a uma velocidade máxima de 166,7 MHz, com um atraso de sinal de 7,5 nanossegundos (ns).Possui 68 pinos de entrada/saída (E/S) que funcionam com a lógica 3.3V e 5V, facilitando o uso em diferentes circuitos.Um recurso essencial é sua programação no sistema 5.0V (ISP) através de uma interface JTAG (IEEE 1149.1).Isso significa que você pode reprogramar sem removê -lo do circuito, facilitando o teste e as atualizações.Ele vem em um pacote de quatro pinos quadrados de 100 pinos (TQFP), que é um pacote compacto de montagem de superfície.Este CPLD é usado em sistemas incorporados, processamento de sinais digitais, dispositivos de comunicação e automação industrial.

Fornecemos componentes de alta qualidade e serviços personalizados, por isso é melhor fazer seu pedido em massa conosco para obter soluções CPLD confiáveis.

Recursos EPM7064STC100-7

• Lógica de alta densidade: O EPM7064STC100-7 foi projetado com 64 macrocélulas e 1.250 portões utilizáveis, tornando-o altamente adequado para implementar funções lógicas complexas em circuitos digitais.Essa arquitetura de alta densidade permite criar projetos de lógica complexos, mantendo a eficiência em operações lógicas programáveis.A estrutura de macrocélula bem otimizada garante a utilização eficaz dos recursos disponíveis, apoiando implementações lógicas combinacionais e seqüenciais avançadas.

• Desempenho rápido: Construído para processamento de alta velocidade, o EPM7064STC100-7 opera com uma frequência interna máxima de 166,7 MHz, permitindo a execução rápida das funções lógicas.Seu atraso de propagação de 7,5 ns garante latência mínima.Essa capacidade de comutação rápida aprimora a capacidade do dispositivo de lidar com o processamento de dados de alta velocidade, condicionamento de sinalização e tarefas de controle com eficiência, tornando-a uma escolha confiável para exigir sistemas digitais.

• E/S versátil: Com 68 pinos de entrada/saída programáveis, o EPM7064STC100-7 oferece flexibilidade excepcional para integração em vários projetos de circuito.Suportando níveis lógicos de 3.3V e 5V, permite compatibilidade contínua com diferentes tensões do sistema, eliminando a necessidade de shifters adicionais de nível de tensão.Essa adaptabilidade o torna adequado para aplicações em ambientes de tensão mista, garantindo ampla aplicabilidade em sistemas incorporados, controles industriais e redes de comunicação.

• Programabilidade no sistema (ISP): Uma das vantagens do EPM7064STC100-7 é a sua programação de 5.0V no sistema (ISP), facilitada por meio de um IEEE STD.1149.1 Interface JTAG.Esse recurso permite reprogramar e modificar as funções lógicas sem dessolir ou remover fisicamente o dispositivo, simplificar a manutenção, a depuração e o desenvolvimento iterativo.A capacidade do ISP reduz o tempo de inatividade e aumenta a flexibilidade das atualizações de firmware, tornando -o inestimável para designs digitais dinâmicos e reconfiguráveis.

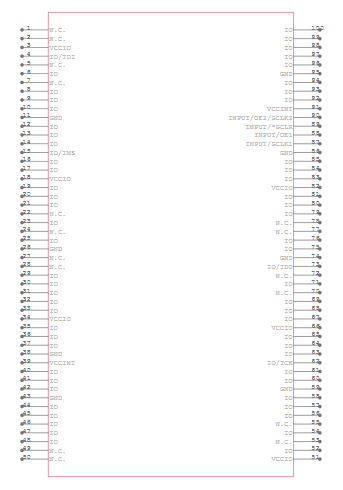

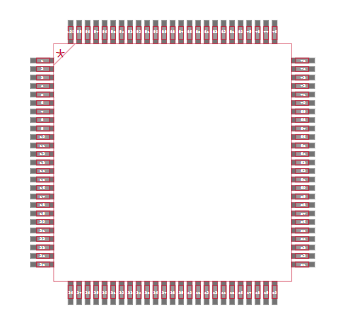

EPM7064STC100-7 Modelos CAD

Símbolo EPM7064STC100-7

EPM7064STC100-7 PESTÃO

Modelo EPM7064STC100-7 3D

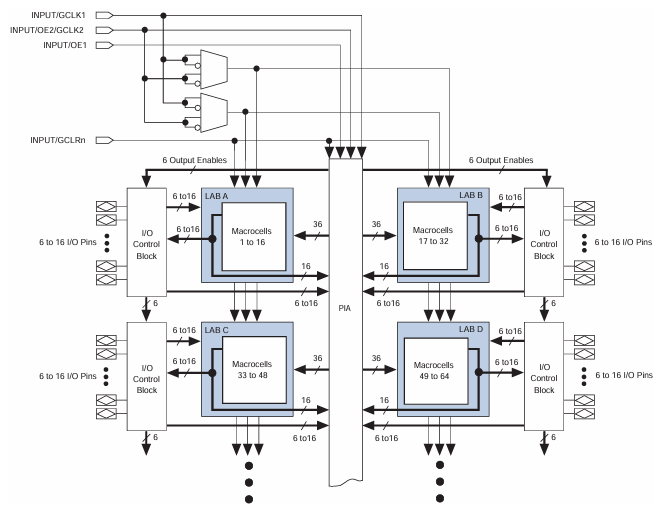

EPM7064STC100-7 Diagrama de blocos

O EPM7064STC100-7 Diagrama de blocos Mostra como os elementos lógicos do chip são conectados e controlados.Possui quatro blocos de matriz lógica (laboratórios), rotulados como A, B, C e D, cada um contendo 16 macrocélulas.Essas macrocélulas desempenham funções lógicas e se conectam através de uma matriz de interconexão programável (PIA), que permite roteamento flexível de sinais.Cada laboratório está vinculado a um bloco de controle de E/S, manuseando até 16 pinos de entrada/saída por laboratório.O diagrama também mostra sinais de controle global (GCLK1, GCLK2, OE1 e GCLRN) que ajudam a gerenciar funções de relógio e redefinição para o chip.Alguns portões lógicos processam esses sinais antes de atingirem diferentes partes do sistema.O design do EPM7064STC100-7 permite que ele seja usado em vários aplicativos lógicos programáveis, como máquinas de estado, decodificação de endereços e outros circuitos digitais personalizados.Suas interconexões flexíveis garantem fluxo de sinal eficiente e operação confiável.

Especificações EPM7064STC100-7

|

Tipo |

Parâmetro |

|

Fabricante |

Altera/Intel |

|

Série |

Max® 7000s |

|

Embalagem |

Bandeja |

|

Status da peça |

Obsoleto |

|

Tipo programável |

No sistema programável |

|

Tempo de atraso tpd (1) max |

7,5 ns |

|

Fornecimento de tensão - interno |

4.75V ~ 5,25V |

|

Número de elementos/blocos lógicos |

4 |

|

Número de macrocélulas |

64 |

|

Número de portões |

1250 |

|

Número de E/S. |

68 |

|

Temperatura operacional |

0 ° C ~ 70 ° C (TA) |

|

Tipo de montagem |

Montagem na superfície |

|

Pacote / caso |

100-TQFP |

|

Pacote de dispositivo de fornecedor |

100-TQFP (14x14) |

|

Número do produto base |

EPM7064 |

EPM7064STC100-7 Sequência de programação no sistema (ISP)

A EPM7064STC100-7, uma parte da família MAX 7000S CPLD, segue uma sequência de programação no sistema de seis estágios (ISP) para garantir a configuração correta.Esse processo permite programar o dispositivo sem removê -lo da placa de circuito.O processo ISP envolve a mudança de instruções, endereços e dados através do pino TDI (Teste de dados em) enquanto recupera as respostas através do pino TDO (Test Data Out).

A primeira etapa, Digite ISP, garante que os pinos de E/S transmitam suavemente do modo de usuário para o modo ISP e requer aproximadamente 1ms.Isso é seguido por Verifique a identificação, onde o ID do silício do dispositivo é lido para confirmar o alvo correto.Em seguida, o Apagar a granel As mudanças de estágio nas instruções de apagar e aplica um pulso de 100ms apagam, limpando todos os dados existentes nas células EEPROM.O Programa O estágio a seguir, onde endereços e dados são deslocados sequencialmente para o dispositivo, aplicando pulsos de programação para configurar as células EEPROM.Cada endereço deve ser programado individualmente, tornando essa etapa demorada, dependendo do número de células EEPROM no dispositivo.

Depois que a programação está concluída, o Verificar O estágio garante que os dados foram armazenados corretamente.Aqui, os pulsos de leitura são aplicados às células EEPROM, e os dados recuperados são comparados aos valores esperados.Se forem encontradas discrepâncias, poderá ser necessária reprogramação.Finalmente, o Saída ISP O estágio garante que os pinos de E/S voltem para o modo de usuário, exigindo outros 1ms.O tempo total de programação ou verificação é influenciado por dois fatores principais: tempo de pulso, necessário para a EEProm apagar, programação e operações de leitura e tempo de mudança, que depende da frequência do TCK (relógio de teste) e do número de ciclos necessários para transferir instruções, endereços e dados.Como diferentes dispositivos com capacidade de ISP têm números variados de células EEPROM, os tempos fixos e variáveis totais são exclusivos para cada dispositivo.O tempo total do ISP pode ser calculado em função da frequência TCK, o número de dispositivos de destino e a arquitetura EEPROM.

Aplicativos EPM7064STC100-7

Sistemas incorporados

O EPM7064STC100-7 é amplamente utilizado em aplicativos de sistema incorporado, onde serve como uma solução lógica programável flexível para controlar vários periféricos, sinais de processamento e implementação de protocolos personalizados.Sua capacidade de interagir com microcontroladores e sensores permite otimizar o desempenho do sistema, mantendo uma pegada compacta.Com sua operação em alta velocidade e baixo consumo de energia, é uma excelente opção para aplicações incorporadas que requerem confiabilidade e eficiência.

Processamento de sinal digital (DSP)

No processamento de sinal digital, o EPM7064STC100-7 desempenha um papel na implementação de filtros, modulação de sinal e várias funções matemáticas.Suas velocidades de comutação rápidas e baixo atraso de propagação o tornam adequado para lidar com tarefas de processamento de dados de alta frequência, garantindo latência mínima na conversão e manipulação de sinal.É comumente usado em processamento de áudio, telecomunicações e sistemas de radar.

Comunicações de dados

O EPM7064STC100-7 é amplamente utilizado em sistemas de rede e comunicação de dados devido à sua capacidade de lidar com operações intensivas em lógica, como roteamento de dados, buffer e correção de erros.Seus recursos de E/S programáveis permitem que ele se adapte a diferentes protocolos de comunicação, tornando -o um componente valioso em interruptores Ethernet, roteadores e infraestrutura de telecomunicações.Seu suporte à programação no sistema (ISP) também permite atualizações de campo, melhorando a adaptabilidade em ambientes dinâmicos de rede.

Automação industrial

As aplicações industriais exigem alta confiabilidade, durabilidade e baixo consumo de energia, tornando o EPM7064STC100-7 uma opção preferida para controladores lógicos programáveis (PLCs), sistemas de controle de motor e equipamentos de teste automatizados.Com sua programação no sistema baseado em JTAG, ele fornece a capacidade de refinar os processos de automação sem a necessidade de remoção física ou redesenho.Sua versatilidade na compatibilidade de tensão também o torna adequado para interface com uma ampla gama de sensores e atuadores usados em ambientes industriais.

EPM7064STC100-7 Peças semelhantes

EPM7064STC100-7 Vantagens

Programabilidade no sistema (ISP)

Uma das maiores vantagens do EPM7064STC100-7 é sua capacidade de ser reprogramada enquanto ainda é montada no sistema.Isso elimina a necessidade de remover o chip para atualizações, reduzir o tempo de manutenção e melhorar a eficiência.Você pode implementar modificações de design sem interromper a produção, tornando-a uma solução econômica para projetos de longo prazo.

Desempenho de alta velocidade

O dispositivo suporta uma alta frequência de operação interna de até 166,7 MHz, permitindo um rápido processamento de dados e tempos de resposta.Isso o torna ideal para aplicações que requerem processamento de sinal, controle lógico e interface de alta velocidade, garantindo operação mais suave e confiável do sistema.

Suporte de E/S versátil

Com até 68 pinos de E/S configuráveis e compatibilidade com vários níveis de tensão (3,3V, 5V e opções tolerantes para 2,5V, 3,3V e 5V), o EPM7064STC100-7 oferece flexibilidade no design do sistema.Ele permite integração perfeita em vários circuitos e suporta ambientes de tensão mista, reduzindo problemas de compatibilidade com outros componentes.

Operação confiável entre ambientes

Projetado para funcionar dentro de uma faixa de temperatura de 0 ° C a 70 ° C, o EPM7064STC100-7 garante operação consistente e estável em uma variedade de condições.Essa confiabilidade o torna uma escolha preferida para aplicações onde a estabilidade ambiental é necessária, como automação industrial, telecomunicações e sistemas de controle incorporados.

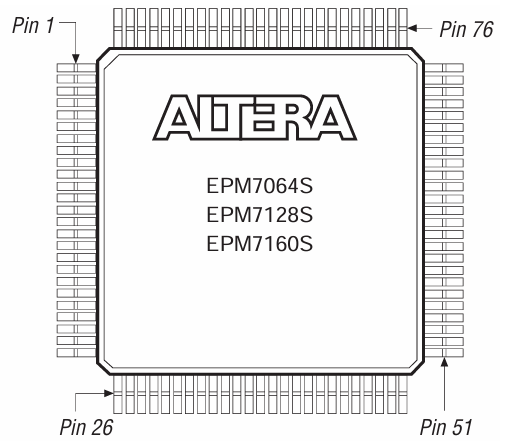

EPM7064STC100-7 Diagrama de identificação de embalagem

O EPM7064STC100-7 é um CPLD (dispositivo lógico programável complexo) da série Max 7000s da Altera, alojada em um pacote Quad Flat de 100 pinos (TQFP-100).Este tipo de pacote foi projetado para aplicações de montagem na superfície, oferecendo um equilíbrio de alta densidade de pinos e tamanho compacto.O Diagrama de identificação Segue um esquema de numeração no sentido anti-horário, com o pino 1 localizado no canto superior esquerdo da embalagem.Movendo -se no sentido anti -horário, os primeiros 25 pinos ocupam o lado esquerdo, os pinos 26 a 50 estão posicionados ao longo da borda inferior, os pinos 51 a 75 continuam ao longo do lado direito e os pinos 76 a 100 são distribuídos ao longo da borda superior.O Pacote TQFP-100 Apresenta cabos finos que se estendem para fora dos quatro lados do corpo plano e quadrado.Esse design aprimora a compatibilidade de montagem de superfície, mantendo o espaçamento adequado para pinos para facilitar a solda e a montagem.O tom de chumbo (distância entre pinos adjacentes) é tipicamente 0,5 mm, otimizando a integridade do sinal e minimizando a pegada geral.

EPM7064STC100-7 Fabricante

O EPM7064STC100-7 é um CPLD (dispositivo lógico programável complexo) originalmente desenvolvido pela Altera, uma empresa de semicondutores conhecida por suas soluções lógicas programáveis.Em 2015, Intel A Altera adquiriu, integrando suas linhas de produtos FPGA e CPLD no grupo de soluções programáveis da Intel (PSG).Desde então, o EPM7064STC100-7 foi marcado sob a Intel, embora tenha sido marcado como obsoleto.A Intel, como fabricante, manteve o suporte herdado aos CPLDs da série Max® 7000s, incluindo esse modelo, enquanto muda gradualmente seu foco para as modernas Technologies Logic FPGA e programável.

Conclusão

O EPM7064STC100-7 reúne funções complexas, desempenho rápido e atualizações fáceis em um chip, provando seu valor em desafiar configurações digitais.Este guia mostrou como funciona, para que é usado e como se encaixa em vários sistemas eletrônicos.Ajuda a fazer os dispositivos funcionarem de maneira suave e eficiente, provando que ainda é muito útil para muitas aplicações.Este guia fornece uma visão clara de como o EPM7064STC100-7 pode ajudar a melhorar os projetos eletrônicos e as operações do sistema de maneira eficaz.

PDF da folha de dados

EPM7064STC100-7 Faixas de dados:

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

perguntas frequentes [FAQ]

1. Como o atraso de propagação de 7,5ns do EPM7064STC100-7 afeta o desempenho do circuito?

Um atraso de propagação de 7,5ns garante processamento de sinal de baixa latência, tornando esse CPLD adequado para aplicações de alta velocidade, como processamento de sinal digital (DSP), sistemas de comunicação e automação industrial que requerem controle de tempo preciso.

2. O EPM7064STC100-7 pode ser programado usando ferramentas de desenvolvimento modernas?

Sim, ele pode ser programado usando o software Quartus II da Intel (anteriormente Altera Quartus) junto com um programador JTAG apropriado.No entanto, o suporte a CPLDs mais antigos como o EPM7064STC100-7 pode ser limitado em versões mais recentes do quartus; portanto, pode ser necessário usar versões herdadas como o Quartus II 13.0 SP1, que ainda suportam dispositivos da série Max® 7000s.

3. Os EPM7064STC100-7 suportam ambientes de tensão mista?

Sim, ele suporta níveis lógicos de 3,3V e 5V, tornando -o compatível com uma ampla gama de circuitos digitais.Essa flexibilidade é útil para interface os componentes de 5V legados com os modernos sistemas de 3.3V sem circuitos adicionais de mudança de nível.

4. Qual é o melhor método para solucionar problemas de um design baseado em EPM7064STC100-7?

Para solucionar problemas, você pode usar o Quartus SignalTap II Analyzer lógico ou os osciloscópios externos e analisadores lógicos para monitorar os sinais.Se a depuração de problemas de programação JTAG, garanta que as conexões TDI, TDO, TCK e TMS estejam corretas e que você esteja usando um programador compatível com blaster USB ou byteblastermv.

5. Posso programar o EPM7064STC100-7 sem removê-lo da minha placa de circuito?

Sim.A programação do sistema 5.0V (ISP) via JTAG (IEEE 1149.1) permite reprogramar o dispositivo enquanto ele permanece no sistema.Isso torna as atualizações, depuração e teste de firmware muito mais eficientes em comparação com os CPLDs tradicionais.

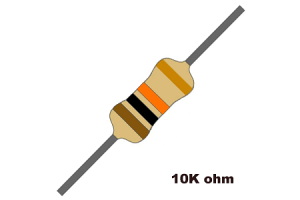

Guia completo para o resistor de 10k: código de cores, aplicativos e usos de circuito

em 10/03/2025

Capacitores vs. baterias: o que é melhor para suas necessidades de energia?

em 07/03/2025

Postagens populares

-

Computadores de conjunto de instruções complexos: como eles mudaram de computação?

em 18/04/8000 147764

-

Pinagem e recursos USB-C

em 18/04/2000 111984

-

Usando o Xilinx Unified Simulation Primitives: um guia abrangente para design e simulação do FPGA

em 18/04/1600 111351

-

Tensões de fonte de alimentação em eletrônica: significado de VCC, VDD, VEE, VSS e GND

em 18/04/0400 83748

-

Guia do conector RJ45: pinagem, fiação, tipos de cabos e usos

em 01/01/1970 79538

-

O guia final para os códigos de cores de arame em sistemas elétricos modernos

A maneira como nossos sistemas elétricos usam cores não é apenas para a aparência.Cada cor do fio agora indica uma função específica, facilitando a identificação e manuseio componentes elétricos co...em 01/01/1970 66949

-

Guia da válvula de purga: função, sintomas, teste e substituição para o desempenho ideal do motor

A válvula de purga é uma parte essencial do sistema de um carro que ajuda a manter o ar limpo, gerenciando vapores de combustível antes que eles possam escapar da atmosfera.Isso não apenas ajuda o ...em 01/01/1970 63087

-

Fator de qualidade (Q): equações e aplicações

O fator de qualidade, ou 'q', é importante ao verificar como os indutores e ressonadores trabalham em sistemas eletrônicos que usam frequências de rádio (RF).'Q' mede o quão bem um circuito minimiz...em 01/01/1970 63028

-

Alcançando o desempenho máximo com o teorema máximo de transferência de energia

O teorema da transferência de energia máxima explica como a energia de uma fonte, como uma bateria ou gerador, flui para uma carga conectada.Ele mostra a condição exata em que a carga recebe mais e...em 01/01/1970 54092

-

A23 Especificações da bateria e compatibilidade

A bateria A23 é uma pequena bateria em forma de cilindro com alta tensão.Também chamado 23A, 23AE, ou MN21, funciona a 12 volts e muito mais alto que as baterias AA ou AAA.Seu design espec...em 01/01/1970 52171