Visão geral do CPLD EPM7512BFC256-5: recursos, especificações e usos

O EPM7512BFC256-5 oferece uma maneira simples de reunir uma grande quantidade de lógica em um dispositivo compacto.Ele armazena sua configuração internamente, de modo que fica pronto para funcionar sempre que você liga seu sistema.Com centenas de macrocélulas, temporização rápida e mais de duzentos pinos de E/S, ele funciona bem quando você deseja substituir peças lógicas dispersas por uma solução limpa.Você pode atualizá-lo através do JTAG sem removê-lo da placa, o que facilita as alterações durante o desenvolvimento ou ajustes posteriores.Seu pacote BGA mantém o layout compacto e ainda oferece bastante liberdade de roteamento.Esteja você construindo equipamentos de comunicação, controladores industriais ou placas compactas incorporadas, este CPLD ajuda a organizar seus sinais sem adicionar peças extras.Catálogo

Visão geral do EPM7512BFC256-5

O EPM7512BFC256-5 é um CPLD de alta densidade da família MAX 7000B, projetado para lidar com controle complexo e lógica de interface em sistemas digitais.Ele oferece cerca de 10.000 portas utilizáveis e 512 macrocélulas, organizadas para suportar decodificação flexível, máquinas de estado e manipulação de barramento em um único dispositivo.O CPLD usa configuração baseada em EEPROM com alimentação interna de 2,5 V, portanto a lógica não é volátil e liga pronta para uso sem memória de configuração externa.Alojado em um pacote FBGA de 256 esferas, ele suporta um grande número de pinos de E/S do usuário, tornando-o adequado para placas densas que exigem muitas terminações de sinal em um espaço compacto.Os usos típicos incluem lógica de colagem, decodificação de endereço, interface de periféricos e personalização de nível de placa em aplicações de comunicação, industriais e incorporadas.Procurando por EPM7512BFC256-5?Entre em contato conosco para verificar o estoque atual, prazo de entrega e preços.

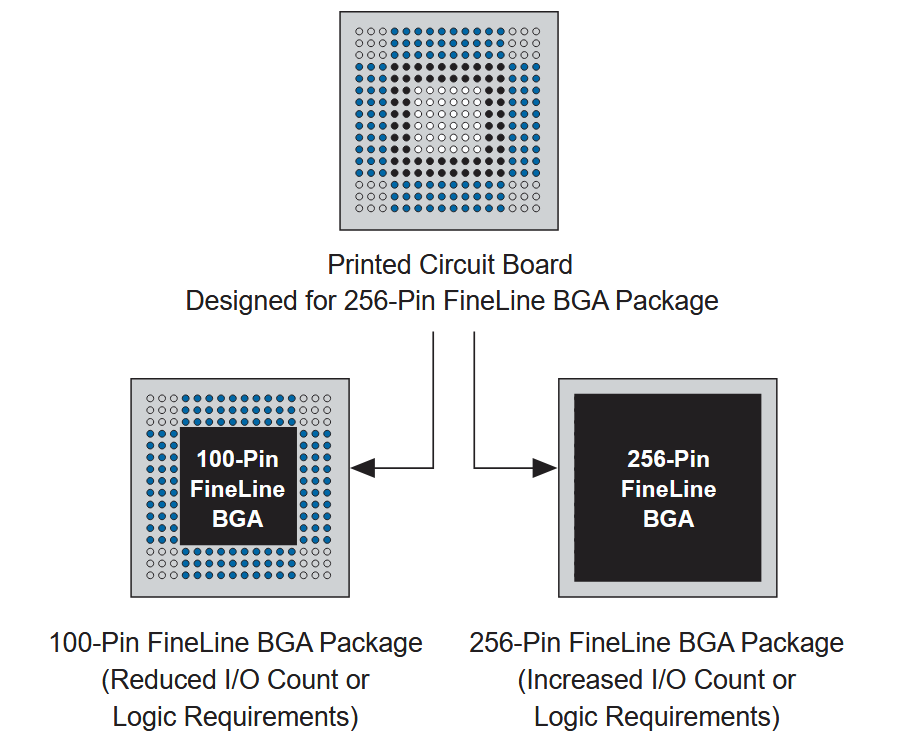

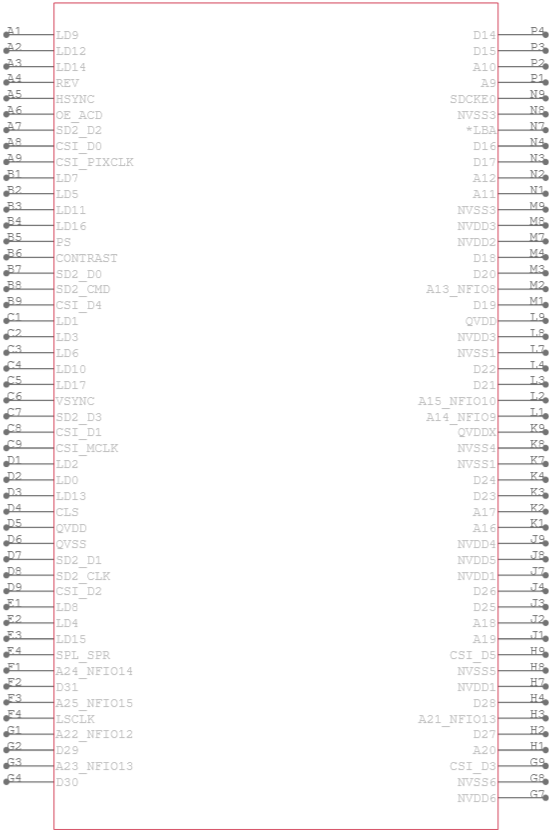

Exemplo de pinagem SameFrame de EPM7512BFC256-5

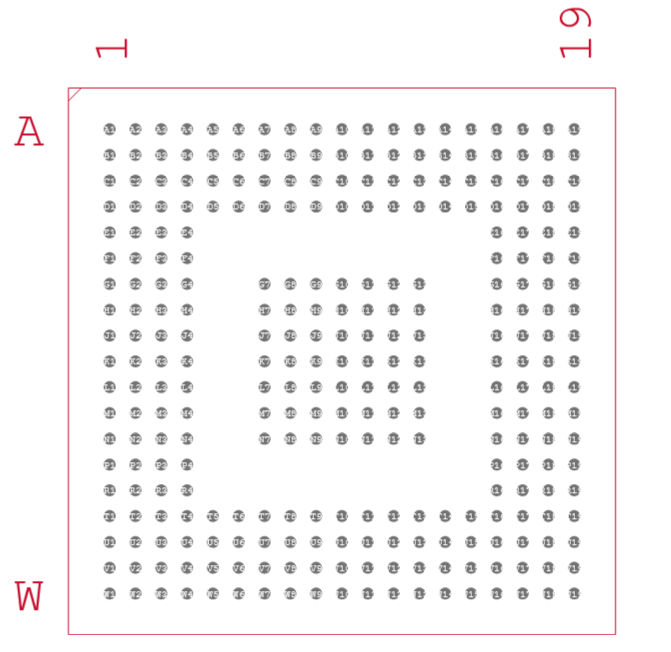

O layout da placa de circuito impresso foi projetado para um pacote FineLine BGA de 256 pinos, enquanto o conceito de pinagem SameFrame alinha um dispositivo FineLine BGA de 100 pinos a um subconjunto das mesmas posições de esfera de solda, permitindo que ambos os pacotes sejam montados no mesmo espaço da placa.A imagem central representa o padrão de terreno comum na placa, e as imagens inferiores rotulam as opções FineLine BGA compatíveis de 100 e 256 pinos, descritas respectivamente como contagem de E/S reduzida e aumentada ou requisitos lógicos.As setas entre a placa e os dois desenhos da embalagem indicam que um layout pode suportar dispositivos com diferentes contagens de pinos, permitindo a migração entre membros da família MAX 7000B, como EPM7512BFC256-5, sem alterar o design da placa subjacente.

Modelo CAD EPM7512BFC256-5

Símbolo EPM7512BFC256-5

Pegada EPM7512BFC256-5

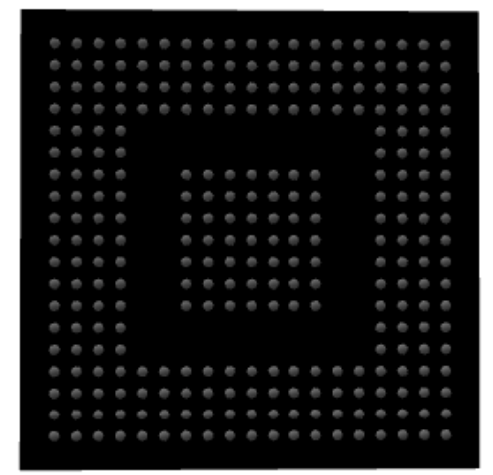

EPM7512BFC256-5 Modelo 3D

Recursos do EPM7512BFC256-5

Arquitetura Lógica Baseada em EEPROM

O EPM7512BFC256-5 usa uma estrutura lógica baseada em EEPROM que armazena dados de configuração dentro do dispositivo.Isso permite que o CPLD seja ligado e pronto para uso sem depender de memória externa, proporcionando um comportamento estável em ciclos repetidos de ativação e desativação.A arquitetura mantém suas funções programadas mesmo quando o sistema está totalmente desligado.

Operação de tensão do núcleo interno

O dispositivo funciona com uma fonte interna que permanece dentro de uma faixa de cerca de 2,375 V a 2,625 V, sendo 2,5 V o nível típico.Esta faixa oferece suporte à operação estável em diferentes condições da placa e ajuda a manter o comportamento de comutação previsível.Também permite que o CPLD funcione em sistemas que seguem práticas de projeto de baixa tensão.

Na programabilidade do sistema através do JTAG

O EPM7512BFC256-5 suporta atualizações através da interface IEEE 1149.1 JTAG, permitindo aos usuários programar ou ajustar o dispositivo enquanto ele permanece soldado à placa.Isto torna prático refinar funções lógicas, verificar a conectividade ou aplicar revisões durante o desenvolvimento e teste.O processo funciona sem remover o CPLD ou interromper os componentes adjacentes.

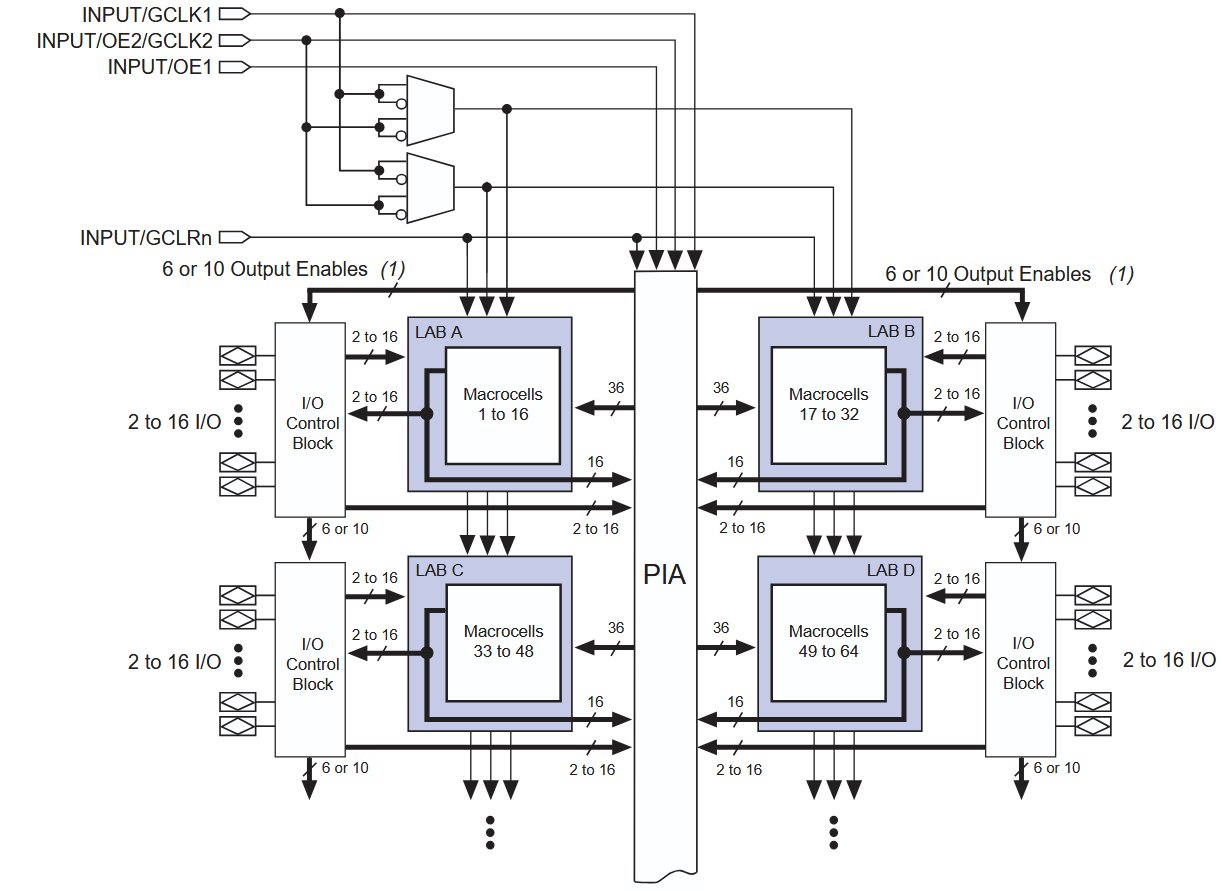

Alta densidade lógica usando macrocélulas e LABs

Um total de 512 macrocélulas são organizadas em 32 blocos de matriz lógica, dando ao dispositivo um layout que lida com muitas camadas de tarefas de controle e decodificação.Cada macrocélula pode ser configurada para suportar uma variedade de funções lógicas, permitindo que os projetistas combinem expressões simples e amplas em um único dispositivo.Esta estrutura ajuda o CPLD a gerenciar grandes conjuntos de sinais relacionados.

Capacidade utilizável do portão para projetos complexos

O EPM7512BFC256-5 fornece cerca de 10.000 portas utilizáveis, oferecendo espaço suficiente para substituir vários componentes lógicos discretos por um dispositivo programável.Essa contagem de portas é adequada para sistemas que necessitam de ampla decodificação, controle de tempo ou comportamento de estado personalizado em uma área compacta.Ele suporta consolidação lógica sem adicionar espaço extra na placa.

Recursos amplos de IO para usuários

Com 212 pinos de E/S do usuário, o dispositivo suporta projetos que exigem muitos pontos de conexão para barramentos, linhas de controle ou interfaces periféricas.A alta contagem de pinos permite o roteamento direto de múltiplos sinais de e para o CPLD sem buffers adicionais.Isso ajuda a simplificar o layout da placa em sistemas densos.

Pacote FBGA compacto 256

O pacote FBGA de 256 bolas usa um layout de 17 por 17 que se adapta bem em placas de circuito compactas.Seu formato de montagem em superfície ajuda a reduzir a altura geral, ao mesmo tempo que fornece caminhos de roteamento claros sob o dispositivo.A área ocupada suporta posicionamento estável e permite espaçamento reduzido entre componentes em montagens modernas.

Características de propagação rápida

O CPLD oferece atrasos de propagação próximos a 5,5 ns, proporcionando comportamento responsivo para caminhos lógicos que necessitam de transições rápidas.Esta temporização suporta aplicações onde os sinais devem passar por vários estágios sem grandes atrasos.Ajuda a manter um fluxo limpo e previsível através de circuitos de controle e interface.

Frequência operacional máxima alta

O dispositivo atinge velocidades operacionais em torno de 160 MHz, com esta classe suportando cerca de 163,9 MHz em uso típico.Esta faixa de frequência permite que o CPLD lide com mudanças rápidas de estado e processos orientados por temporização.Ele funciona bem em sistemas onde os sinais de controle são atualizados em taxas mais altas.

Conformidade de temperatura comercial

A faixa operacional de 0°C a 70°C suporta o uso estável em ambientes internos típicos.O dispositivo mantém seu comportamento e temporização programados em toda essa faixa, tornando-o adequado para equipamentos comerciais padrão.Esta janela de temperatura cobre a sala comum até as condições quentes observadas em sistemas fechados.

Especificações Técnicas EPM7512BFC256-5

| Atributo do produto | Valor do Atributo |

| Fabricante | Informações |

| Alimentação de Tensão - Interna | 2,375 V ~ 2,625 V |

| Pacote de dispositivos do fornecedor | 256-FBGA (17x17) |

| Série | MAX®7000B |

| Tipo programável | Em sistema programável |

| Pacote/Caso | 256-BGA |

| Pacote | Bandeja |

| Temperatura operacional | 0°C ~ 70°C (TA) |

| Número de macrocélulas | 512 |

| Número de elementos/blocos lógicos | 32 |

| Número de E/S | 212 |

| Número de portões | 10.000 |

| Tipo de montagem | Montagem em superfície |

| Tempo de atraso tpd(1) Máx. | 5,5ns |

| Número básico do produto | EPM7512 |

Diagrama de blocos do dispositivo MAX 7000B de EPM7512BFC256-5

A arquitetura interna do EPM7512BFC256-5 é organizada em torno de vários blocos de matriz lógica, cada um contendo grupos de macrocélulas vinculadas por uma matriz central de interconexão programável que roteia sinais entre a lógica e a E/S.As entradas globais rotuladas como clock, clear e habilitação de saída alimentam uma pequena rede de controle na parte superior do diagrama, que distribui sinais de controle compartilhados para cada bloco lógico e seção de E/S.Cada lado do dispositivo inclui blocos de controle de E/S conectados a pinos externos, mostrados como faixas como “2 a 16 E/S”, com conexões locais em blocos de matriz lógica próximos e acesso mais amplo através da matriz de interconexão.As linhas de habilitação de saída indicadas como “6 ou 10 habilitações de saída” se espalham em direção às estruturas de E/S, permitindo que grupos de saídas compartilhem o controle de habilitação.As notas abaixo da figura explicam que os membros da mesma família podem suportar contagens diferentes dessas linhas de habilitação compartilhadas, confirmando que o diagrama representa a organização interna comum usada pelos dispositivos MAX 7000B, incluindo o EPM7512BFC256-5.

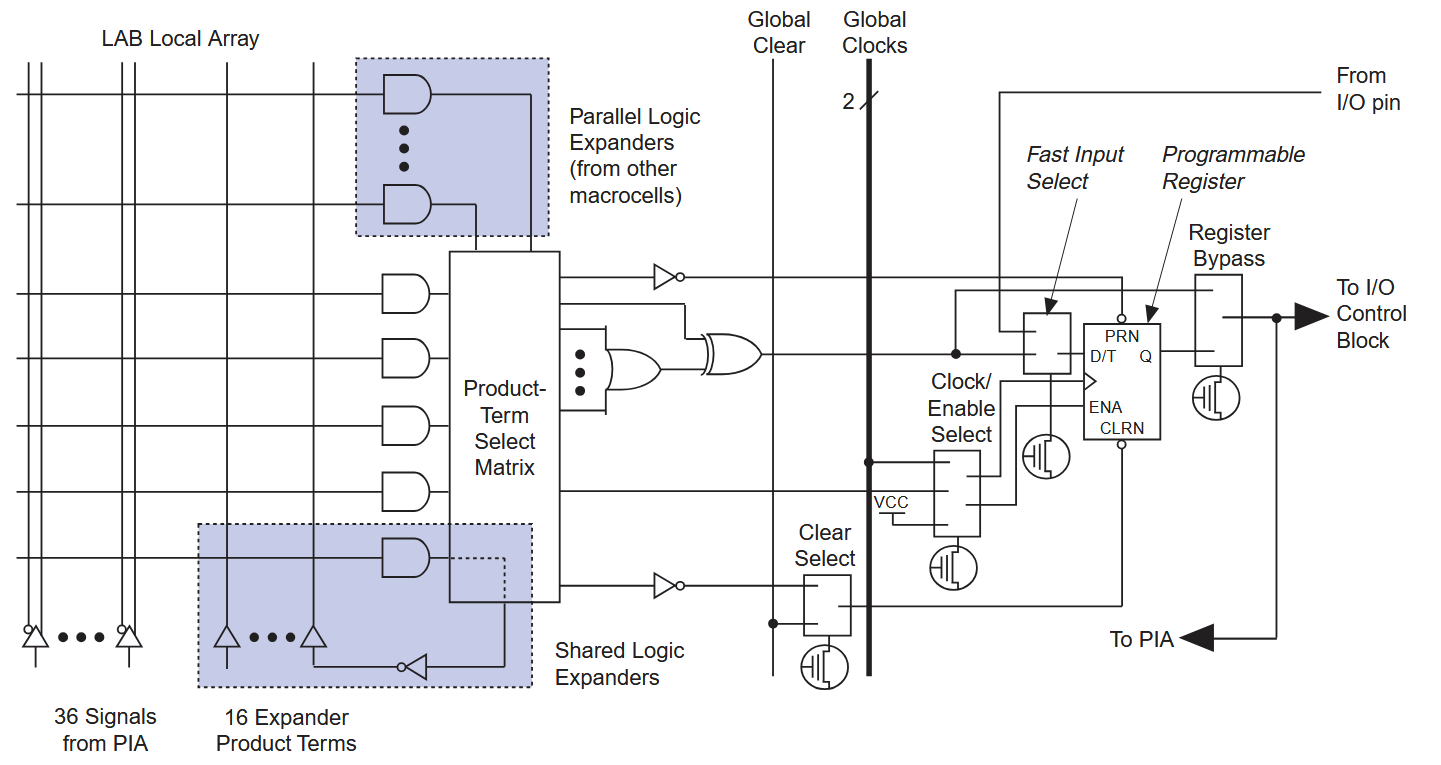

Macrocélula MAX 7000B de EPM7512BFC256-5

A estrutura de macrocélula para EPM7512BFC256-5 combina um array local LAB à esquerda, onde 36 sinais do array de interconexão programável e 16 termos de produto expansor alimentam uma matriz de seleção de termo de produto e expansores lógicos compartilhados, com uma seção de controle e registro à direita que gerencia clocking, compensação e roteamento de dados.Expansores lógicos paralelos de macrocélulas vizinhas unem-se aos sinais locais para formar a soma dos produtos que acionam a porta lógica principal, que então se conecta a um registro programável que pode ser ignorado para operação puramente combinatória.A limpeza global e duas linhas de relógio global entram em circuitos de seleção dedicados, permitindo a seleção independente de entrada rápida, fonte de clock ou habilitação e comportamento de limpeza para cada macrocélula.A saída registrada ou combinacional aciona o bloco de controle de E/S e o conjunto de interconexão programável, enquanto um caminho de entrada rápido opcional do pino de E/S externo fornece uma conexão direta à seção de registro para tratamento de sinal de baixa latência.

Aplicações de EPM7512BFC256-5

Sistemas de Telecomunicações e Redes

O EPM7512BFC256-5 é amplamente utilizado em switches de rede, módulos de comunicação e plataformas de telecomunicações que dependem de recursos lógicos densos para gerenciar múltiplas interfaces.Ele pode lidar com coordenação de barramento, controle de tempo e roteamento de sinal em sistemas onde muitos caminhos de dados devem operar juntos.Sua configuração não volátil permite que o dispositivo retenha lógica personalizada para manipulação de protocolo e gerenciamento de sistema durante ciclos de energia.

Subsistemas de controle eletrônico automotivo

Os subsistemas automotivos que operam dentro dos limites comerciais de temperatura podem usar este CPLD para gerenciar sinais de controle e suportar funções lógicas personalizadas.Ele se adapta a aplicações onde a consolidação lógica compacta ajuda a reduzir a complexidade da placa, como pequenas unidades de controle ou blocos de condicionamento de sinais.O dispositivo mantém um comportamento estável em partidas repetidas, tornando-o adequado para unidades que realizam ciclos com frequência.

Automação Industrial e Controle de Fábrica

Em ambientes industriais, o dispositivo suporta tarefas como controle de máquina de estado, mapeamento de E/S e pequenas funções de protocolo que ajudam a coordenar o comportamento do equipamento.Seu tempo previsível e configuração pronta para inicialização funcionam bem em sistemas que funcionam por longos períodos ou reiniciam em intervalos regulares.Isto o torna uma escolha prática para controladores, unidades de monitoramento e módulos de automação.

Eletrônicos de consumo e embarcados

O dispositivo é adequado para produtos embarcados que necessitam de lógica programável para gerenciar a coordenação interna entre subsistemas.Ele pode suportar adaptação de interface, controle de tempo básico e organização de sinal personalizada em placas compactas.Sua capacidade de armazenar lógica internamente ajuda a manter o comportamento do sistema consistente sem adicionar peças de memória externa.

Suporte a sistemas legados e manutenção de design

Muitos projetos mais antigos usam a família MAX 7000B, e o EPM7512BFC256-5 pode servir como um substituto direto nesses sistemas.Ele suporta manutenção contínua, reparos e atualizações graduais sem alterar a arquitetura geral da placa.Isso permite o uso contínuo de projetos estabelecidos, mantendo o hardware alinhado com os componentes disponíveis.

Vantagens e desvantagens do EPM7512BFC256-5

Vantagens

• Alta densidade lógica com 512 macrocélulas e cerca de 10 mil portas utilizáveis suporta ampla integração de sistema

• A configuração baseada em EEPROM permite atualizações e ajustes enquanto o dispositivo permanece na placa

• Resposta rápida pino a pino e temporização estável suportam caminhos digitais de alta velocidade

• Ampla contagem de E/S e um pacote FBGA de 256 bolas permitem roteamento flexível para projetos densos

• A compatibilidade de pinos na família MAX 7000B suporta a reutilização de layouts de design existentes

• A configuração não volátil elimina a necessidade de um dispositivo de memória externo

• Família de dispositivos bem estabelecida com recursos técnicos acessíveis

Desvantagens

• Não classificado para requisitos sem chumbo, o que pode limitar o uso em alguns ambientes regulamentados

• A faixa de temperatura comercial de 0°C a 70°C pode não ser adequada para aplicações de temperatura mais amplas

• Usa níveis de processo mais antigos de 2,5 V e 3,3 V, o que pode levar a um uso de energia maior do que as famílias lógicas mais recentes

• O pacote BGA grande pode exceder as necessidades de projetos que exigem menos pinos

Alternativas EPM7512BFC256-5

| Número da peça | Fabricante | Principais recursos | Caso de uso/Notas |

| EPM7512BFC256-5N | Informações | CPLD MAX® 7000B com 512 macrocélulas e cerca de 10 mil portas utilizáveis.Arquitetura EEPROM programável no sistema, pacote FBGA de 256 esferas com alta contagem de E/S e fonte de núcleo de baixa tensão adequada para projetos modernos de 2,5 V. | Bom para lógica adesiva, máquinas de estado simples e expansão de E/S.Útil em projetos de atualização legados onde são preferidos fluxos de ferramentas MAX 7000B e espaços BGA compatíveis com pinos. |

| EPM7512BFC256-5GZ | Informações | Mesma capacidade lógica e recursos ISP do MAX® 7000B com uma variante sem chumbo e compatível com RoHS.256-BGA de alta densidade, ampla disponibilidade de E/S e temporização estável adequado para tarefas de controle e interface. | Uma escolha imediata para construções em conformidade com o meio ambiente.Adapta-se a controle digital denso, backplanes de comunicação e projetos com espaço limitado de placa que necessitam de muitos pinos de E/S. |

| EPM7512BFC256-7 | Informações | CPLD MAX® 7000B com 512 macrocélulas e programabilidade no sistema.Oferece o mesmo espaço de 256 BGA e recursos de E/S, com um nível de velocidade ajustado para tempo e potência equilibrados. | Adequado para lógica de controle sensível ao custo, interfaces de velocidade moderada e variantes de produtos onde não é necessária velocidade mais restrita, mas a compatibilidade da placa e da ferramenta deve ser mantida. |

Sobre a Intel

Intel é uma grande empresa de semicondutores com sede nos Estados Unidos, fundada em 1968 e sediada em Santa Clara, Califórnia.Você trabalha com um fornecedor cujos principais produtos incluem microprocessadores, chipsets, dispositivos lógicos programáveis e outros circuitos integrados usados em sistemas de computação e comunicação.Através de suas linhas lógicas programáveis, que incluem CPLDs e FPGAs, a Intel oferece suporte a projetos que vão desde controle embarcado até processamento de dados e sinais.Sua longa história em design de dispositivos e fabricação de alto volume fornece um contexto estável para peças como o EPM7512BFC256-5 em sistemas de sinais digitais e mistos.

Conclusão

O EPM7512BFC256-5 reúne velocidade, flexibilidade e uma grande quantidade de lógica em um único dispositivo.Você obtém um CPLD que inicia instantaneamente, lida com muitos sinais e é fácil de atualizar por meio do JTAG.Sua arquitetura suporta ampla decodificação, máquinas de estado e lógica de interface sem a necessidade de componentes extras.Você pode encaixá-lo em uma variedade de sistemas, desde hardware de comunicação até placas incorporadas, e confiar em seu tempo constante e comportamento claro.Com seu pacote BGA compacto e alta contagem de E/S, ele oferece espaço para expandir seu design enquanto mantém o layout gerenciável.No geral, oferece uma maneira confiável de controlar e organizar sinais digitais em muitos tipos de projetos.

Folha de dados PDF

Folha de dados EPM7512BFC256-5:

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

perguntas frequentes [FAQ]

1. O que o EPM7512BFC256-5 faz principalmente?

Ele lida com tarefas lógicas personalizadas dentro de um sistema digital.Você pode usá-lo para gerenciar máquinas de estado, decodificação, controle de tempo e funções relacionadas ao barramento.Ele ajuda você a substituir muitas peças lógicas pequenas por um dispositivo programável.

2. O EPM7512BFC256-5 pode ser atualizado enquanto está na placa?

Sim.Ele suporta programação no sistema por meio de JTAG, para que você possa atualizar ou ajustar sua lógica sem removê-la.Isso torna os testes e o ajuste muito mais fáceis.

3. Quantos pinos de E/S este CPLD oferece?

Ele fornece 212 pinos de E/S de usuário, oferecendo bastante espaço para barramentos, linhas de controle e conexões de interface.Isso o torna útil em projetos que necessitam de muitos caminhos de sinal.

4. Quais tensões de alimentação ele utiliza?

O dispositivo usa uma fonte de alimentação interna de 2,5 V e normalmente funciona com E/S de 3,3 V.Isso corresponde a muitos sistemas digitais comuns e mantém o design simples.

5. Onde o EPM7512BFC256-5 é comumente usado?

Você pode encontrá-lo em equipamentos de telecomunicações, controladores industriais, produtos embarcados e sistemas mais antigos que utilizam a família MAX 7000B.Sua configuração não volátil e amplo suporte de E/S o tornam útil em muitos tipos de placas digitais.

Por que o EPF10K30EFC256-2 funciona bem em projetos digitais de médio porte

em 05/12/2025

Explicação do meio subtrator: portas lógicas, circuito, tabela verdade e aplicações

em 04/12/2025

Postagens populares

-

Computadores de conjunto de instruções complexos: como eles mudaram de computação?

em 18/04/8000 147758

-

Pinagem e recursos USB-C

em 18/04/2000 111948

-

Usando o Xilinx Unified Simulation Primitives: um guia abrangente para design e simulação do FPGA

em 18/04/1600 111349

-

Tensões de fonte de alimentação em eletrônica: significado de VCC, VDD, VEE, VSS e GND

em 18/04/0400 83722

-

Guia do conector RJ45: pinagem, fiação, tipos de cabos e usos

em 01/01/1970 79508

-

O guia final para os códigos de cores de arame em sistemas elétricos modernos

A maneira como nossos sistemas elétricos usam cores não é apenas para a aparência.Cada cor do fio agora indica uma função específica, facilitando a identificação e manuseio componentes elétricos co...em 01/01/1970 66918

-

Guia da válvula de purga: função, sintomas, teste e substituição para o desempenho ideal do motor

A válvula de purga é uma parte essencial do sistema de um carro que ajuda a manter o ar limpo, gerenciando vapores de combustível antes que eles possam escapar da atmosfera.Isso não apenas ajuda o ...em 01/01/1970 63076

-

Fator de qualidade (Q): equações e aplicações

O fator de qualidade, ou 'q', é importante ao verificar como os indutores e ressonadores trabalham em sistemas eletrônicos que usam frequências de rádio (RF).'Q' mede o quão bem um circuito minimiz...em 01/01/1970 63012

-

Alcançando o desempenho máximo com o teorema máximo de transferência de energia

O teorema da transferência de energia máxima explica como a energia de uma fonte, como uma bateria ou gerador, flui para uma carga conectada.Ele mostra a condição exata em que a carga recebe mais e...em 01/01/1970 54081

-

A23 Especificações da bateria e compatibilidade

A bateria A23 é uma pequena bateria em forma de cilindro com alta tensão.Também chamado 23A, 23AE, ou MN21, funciona a 12 volts e muito mais alto que as baterias AA ou AAA.Seu design espec...em 01/01/1970 52145