Visão geral do chip lógico programável EPM7128ATC100-10

Trabalhar com sistemas digitais muitas vezes significa que você precisa de uma lógica flexível que possa se adaptar a diferentes caminhos de sinal e tarefas de controle.EPM7128ATC100-10 oferece uma solução lógica programável que pode ser configurada para gerenciar temporização, roteamento e controle lógico dentro de sistemas eletrônicos.Com 128 macrocélulas e milhares de portas lógicas utilizáveis, você pode criar funções lógicas personalizadas dentro de um dispositivo compacto.Seu pacote de montagem em superfície cabe facilmente em placas de circuito modernas, enquanto a temporização estável e as conexões flexíveis de entrada e saída ajudam você a lidar com muitos tipos de tarefas de controle digital em sistemas embarcados.Catálogo

Visão geral do EPM7128ATC100-10

EPM7128ATC100-10 é um dispositivo lógico programável projetado para implementar funções de controle digital configuráveis em sistemas eletrônicos embarcados.O dispositivo contém 128 macrocélulas e aproximadamente 2.500 portas lógicas que permitem aos projetistas criar circuitos lógicos personalizados, como lógica de controle, gerenciamento de interface e máquinas de estado.Sua estrutura organiza a lógica programável em vários blocos de matriz lógica conectados por meio de uma rede de roteamento interna que distribui sinais por todo o dispositivo.Operando em uma faixa de alimentação de 3 V a 3,6 V e suportando atraso de propagação de até 10 ns, ele permite temporização lógica previsível.O pacote TQFP de 100 pinos suporta instalação compacta de montagem em superfície em projetos de circuito com espaço limitado.

Procurando por EPM7128ATC100-10?Entre em contato conosco para verificar o estoque atual, prazo de entrega e preços.

Configuração de pinos de EPM7128ATC100-10

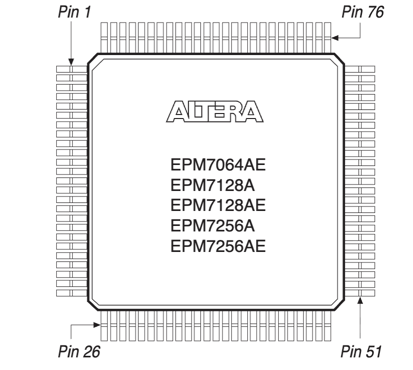

O layout da embalagem quadrada apresenta um dispositivo de estilo quádruplo plano com cabos de metal que se estendem de todos os quatro lados do corpo.Os números dos pinos são organizados sequencialmente ao redor do perímetro, começando com o pino 1 no canto superior esquerdo e continuando ao longo de cada lado em ordem até que os pinos finais apareçam nas bordas restantes.Os indicadores de canto marcam os principais pontos de orientação usados para o posicionamento correto do dispositivo em uma placa de circuito impresso.A área central contém marcações de identificação de dispositivos associadas à família de lógica programável MAX 7000A.O espaçamento dos cabos e o arranjo simétrico suportam a instalação de montagem em superfície e permitem que cada pino externo se conecte ao roteamento de sinal na placa.

Exemplo de pinagem de EPM7128ATC100-10

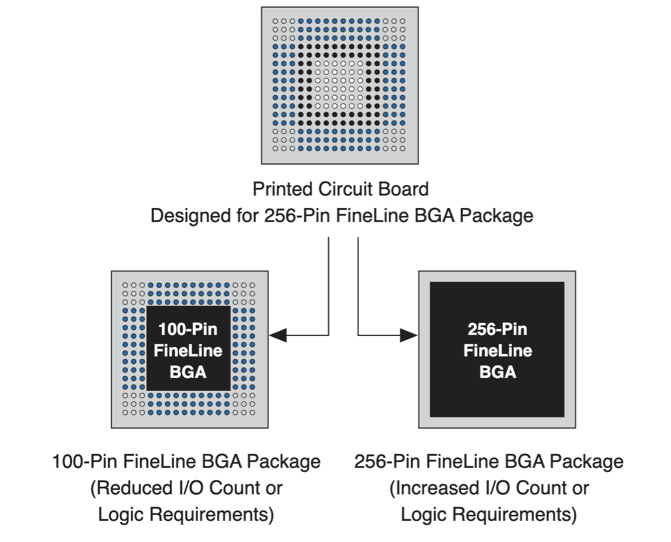

A disposição dos pinos demonstra um layout de placa de circuito impresso compartilhado que suporta vários tamanhos de pacote FineLine BGA.Um design de placa central originalmente preparado para uma pegada FineLine BGA de 256 pinos é mostrado com uma grade densa de localizações de esferas de solda.O layout permite que um dispositivo FineLine BGA menor de 100 pinos seja colocado dentro do mesmo campo de pinos, mantendo conexões de roteamento compatíveis.As posições externas da esfera permanecem sem uso quando o pacote menor é instalado, enquanto a grade completa é utilizada para o dispositivo maior.Este arranjo permite que um design de placa única suporte dispositivos com diferentes contagens de entrada e saída ou requisitos lógicos sem alterar o layout da PCB.

Recursos do EPM7128ATC100-10

Arquitetura Lógica Programável

O dispositivo usa uma estrutura lógica programável baseada em macrocélulas que permite que circuitos digitais sejam configurados após a fabricação.Cada macrocélula pode implementar lógica combinacional ou funções lógicas registradas, dando aos projetistas flexibilidade ao construir caminhos de controle, lógica de roteamento de sinal e circuitos de temporização.Esta arquitetura permite que diversas funções lógicas discretas sejam integradas em um dispositivo, mantendo um comportamento lógico previsível.

Blocos de matriz lógica estruturada

Os recursos lógicos internos são organizados em blocos de matriz lógica que agrupam macrocélulas e compartilham recursos de roteamento.Este arranjo simplifica a distribuição interna do sinal e ajuda a manter a operação lógica estável em todo o dispositivo.Os sinais podem ser roteados entre blocos através de uma rede de interconexão interna que suporta arranjos lógicos digitais complexos.

Ampla conectividade de entrada e saída

Até oitenta e quatro pinos de entrada e saída permitem que o dispositivo se conecte diretamente a vários sinais digitais em um sistema embarcado.Esses pinos podem ser configurados para operação de entrada, saída ou bidirecional, dependendo dos requisitos do projeto.Essa flexibilidade permite que o dispositivo gerencie a comunicação entre processadores, dispositivos de memória e circuitos lógicos periféricos.

Resposta Lógica Rápida

O dispositivo suporta atraso de propagação de até dez nanossegundos, permitindo um comportamento lógico digital responsivo.Este desempenho de temporização suporta funções de controle que exigem comutação de sinal consistente e sincronização confiável com outros componentes digitais no sistema.

Lógica Eletricamente Reprogramável

A configuração é armazenada usando tecnologia programável apagável eletricamente que permite que a lógica do dispositivo seja atualizada quando os requisitos do sistema mudam.Os projetistas podem modificar a lógica digital durante o desenvolvimento ou manutenção do sistema sem substituir o componente de hardware.

Operação em Baixa Tensão

A operação dentro de uma faixa de alimentação de três volts a três vírgula seis volts permite que o dispositivo se integre a muitos sistemas digitais modernos.Esta faixa de tensão suporta níveis lógicos estáveis, mantendo a compatibilidade com padrões comuns de interface digital.

Pacote compacto de montagem em superfície

O dispositivo é fornecido em um pacote plano quádruplo fino de cem pinos projetado para montagem em superfície.O tamanho compacto da embalagem ajuda a economizar espaço na placa e oferece suporte a processos de fabricação automatizados usados na produção eletrônica moderna.

Capacidade de controle digital integrado

A combinação de lógica programável, roteamento flexível e conexões de entrada e saída configuráveis permite que o dispositivo execute diversas tarefas de controle digital.Ele pode substituir vários circuitos lógicos discretos, mantendo o comportamento estável do sinal em projetos eletrônicos incorporados.

Especificações Técnicas EPM7128ATC100-10

| Atributo do produto | Valor do Atributo |

| Fabricante | Altera (Intel) |

| Alimentação de Tensão - Interna | 3V ~ 3,6V |

| Pacote de dispositivos do fornecedor | 100-TQFP (14x14) |

| Série | MAX®7000A |

| Tipo programável | EE PLD |

| Pacote/Caixa | 100-TQFP |

| Pacote | Massa |

| Temperatura operacional | 0°C ~ 70°C (TA) |

| Número de macrocélulas | 128 |

| Número de elementos/blocos lógicos | 8 |

| Número de E/S | 84 |

| Número de portões | 2500 |

| Tipo de montagem | Montagem em superfície |

| Tempo de atraso tpd(1) Máx. | 10 ns |

| Número básico do produto | EPM7128 |

| Status RoHS | RoHS não compatível |

| Nível de sensibilidade à umidade (MSL) | 3 (168 horas) |

| Estado do REACH | REACH não afetado |

| ECCN | EAR99 |

| HTSU | 8542.39.0001 |

Diagrama de blocos do dispositivo EPM7128ATC100-10

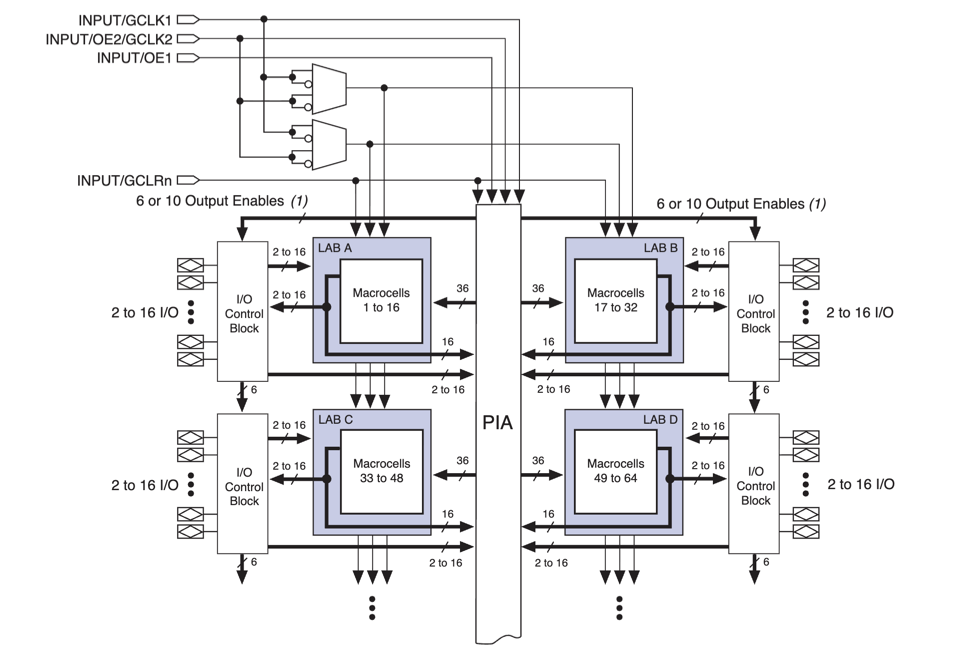

O diagrama ilustra a arquitetura lógica interna usada pelos dispositivos CPLD MAX 7000A, como o EPM7128ATC100-10.A estrutura é organizada em torno de vários blocos de matriz lógica rotulados como LAB A, LAB B, LAB C e LAB D, cada um contendo grupos de macrocélulas que implementam funções lógicas programáveis.Essas macrocélulas suportam lógica combinacional e operações lógicas registradas dentro do dispositivo.Os blocos da matriz lógica são conectados por meio de uma matriz central de interconexão programável que roteia sinais entre seções lógicas.Cada bloco de matriz lógica se conecta a um bloco de controle de E/S que gerencia os pinos de entrada e saída do dispositivo.Sinais de controle globais, incluindo entradas de relógio, sinais de habilitação de saída e entradas claras globais, entram pela parte superior da arquitetura e distribuem sinais de controle pela estrutura lógica interna para coordenar a operação do dispositivo.

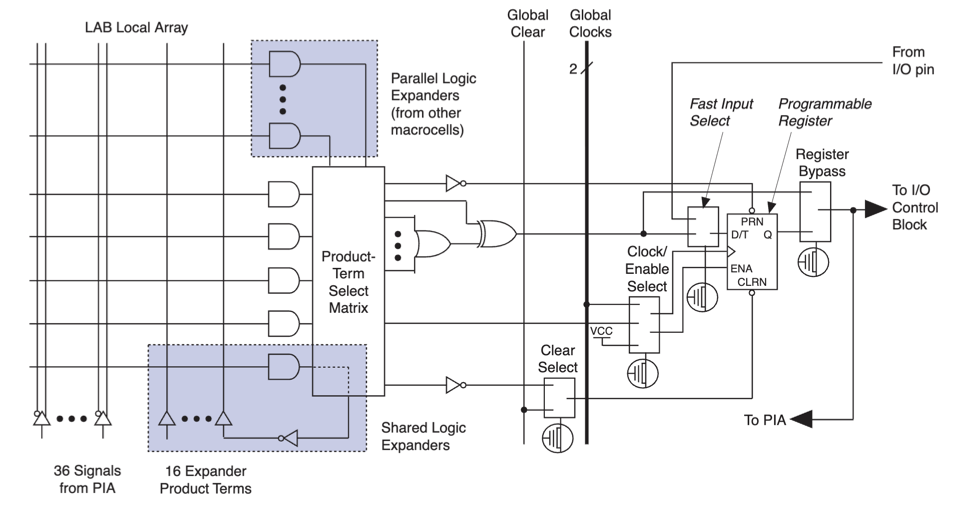

Macrocélula de EPM7128ATC100-10

Os sinais lógicos entram na macrocélula a partir da matriz de interconexão programável através de trinta e seis linhas de roteamento conectadas à matriz local LAB.Uma matriz de seleção de termos de produto combina esses sinais com até dezesseis termos de produto expansores para criar funções lógicas programáveis.Os expansores lógicos paralelos permitem termos adicionais de macrocélulas vizinhas, enquanto os expansores lógicos compartilhados distribuem termos extras do produto através do bloco da matriz lógica para aumentar a capacidade lógica.Os caminhos de saída alimentam um registro programável que opera com relógio global e linhas de controle claras, permitindo saída registrada ou combinatória direta.Um caminho de seleção de entrada rápida aceita sinais de um pino de E/S externo, e um caminho de desvio de registro permite que o sinal passe sem armazenamento com clock.Os sinais de saída finais são roteados para o bloco de controle IO para pinos externos ou de volta para o Programmable Interconnect Array para roteamento de sinal interno.

Aplicações de EPM7128ATC100-10

Lógica de controle de sistema embarcado

Dispositivos lógicos programáveis como este são frequentemente usados para implementar lógica de controle personalizada dentro de sistemas embarcados.Ele pode coordenar relações de temporização entre processadores, sensores e dispositivos de comunicação, mantendo ao mesmo tempo um fluxo de sinal estável em todo o sistema.

Controladores de automação industrial

Equipamentos de automação frequentemente requerem lógica dedicada para gerenciar sensores, relés e sinais de atuadores.O dispositivo pode ser programado para lidar com sequências de controle, verificações de segurança e tarefas de roteamento de sinais usadas em máquinas automatizadas e sistemas de monitoramento.

Lógica de Interface de Telecomunicações

Equipamentos de comunicação usam lógica programável para gerenciar o roteamento de sinais entre processadores e circuitos de interface.O dispositivo pode suportar comutação digital, manipulação de protocolo e condicionamento de sinal que ajudam a manter uma comunicação confiável entre os componentes do sistema.

Circuitos de controle de eletrônicos de consumo

Os produtos digitais de consumo muitas vezes dependem de dispositivos lógicos compactos para coordenar as operações internas.O dispositivo pode gerenciar temporização, processamento de entrada e controle de sinal em produtos eletrônicos, como equipamentos multimídia, eletrodomésticos e dispositivos periféricos.

Roteamento de sinal digital e gerenciamento de interface

Sistemas que combinam vários subsistemas digitais requerem roteamento controlado de sinal entre componentes.A estrutura lógica programável permite que os projetistas criem uma lógica de roteamento personalizada que direciona sinais entre memória, processadores e interfaces externas.

Implementação de Máquina de Estado

Muitos sistemas eletrônicos dependem de máquinas de estado para gerenciar sequências operacionais.O dispositivo pode implementar essas estruturas de controle baseadas em estado usando caminhos lógicos programáveis que respondem às condições de entrada e eventos de temporização.

Substituição de componentes lógicos discretos

Várias portas lógicas e circuitos de controle separados podem muitas vezes ser consolidados em um dispositivo programável.Essa abordagem reduz a complexidade da placa e permite que o comportamento lógico seja ajustado por meio de atualizações de configuração quando os requisitos do sistema mudam.

Vantagens e desvantagens do EPM7128ATC100-10

Vantagens

• Lógica programável flexível permite que os projetistas implementem circuitos digitais personalizados

• Ciclo de desenvolvimento mais rápido em comparação com dispositivos lógicos fixos

• Integração compacta de múltiplas funções lógicas em um único dispositivo

• Operação confiável com atraso de propagação relativamente baixo para tarefas de lógica de controle

• Suporta múltiplas conexões de entrada e saída através de 84 pinos de E/S

• Arquitetura reprogramável permite atualizações de design durante o desenvolvimento

• Adequado para substituir vários ICs lógicos discretos em sistemas embarcados

Desvantagens

• Menor densidade lógica em comparação com dispositivos FPGA modernos

• Recursos internos limitados em relação às famílias lógicas programáveis mais recentes

• Faixa de temperatura operacional restrita em comparação com dispositivos de nível industrial

• A versão não compatível com RoHS pode limitar o uso em alguns projetos modernos de conformidade ambiental

Alternativas EPM7128ATC100-10

| Número da peça | Fabricante | Principais recursos | Caso de uso/Notas |

| EPM7128ATC100-12F | Altera | CPLD da família MAX 7000A com 128 macrocélulas e aproximadamente 2.500 portas lógicas utilizáveis.Usa tecnologia lógica programável apagável eletricamente e um pacote TQFP de 100 pinos com muitas conexões de E/S programáveis. | Usado para lógica de controle digital, lógica de interface de barramento e lógica de colagem de sistema onde diversas funções digitais devem ser implementadas em um dispositivo programável. |

| EPM7128ATC100-6 | Altera | CPLD de maior velocidade da arquitetura MAX 7000A.Fornece macrocélulas programáveis, recursos de roteamento interno e pinos flexíveis de entrada e saída digital. | Adequado para lógica digital sensível ao tempo, gerenciamento de interface e sistemas de controle integrados que exigem resposta lógica mais rápida. |

| EPM7128ATC144-10 | Altera | Dispositivo CPLD usando arquitetura MAX 7000A com memória de configuração não volátil e um pacote maior que suporta mais conexões de E/S para integração de sistema digital. | Comum em placas de controle industriais, hardware de comunicação e tarefas de controle lógico programável onde sinais externos adicionais devem ser tratados. |

Sobre Altera (Intel)

Altera era uma empresa de semicondutores conhecida por desenvolver dispositivos lógicos programáveis usados em sistemas digitais e eletrônicos embarcados.A empresa se especializou em matrizes de portas programáveis em campo e dispositivos lógicos programáveis complexos que permitem aos projetistas implementar circuitos digitais personalizados em um único componente.Suas famílias de produtos foram amplamente utilizadas em equipamentos de comunicação, plataformas de computação, sistemas de controle industrial e eletrônicos de consumo.Em 2015, a empresa tornou-se parte da Intel, onde suas tecnologias de lógica programável continuam a ser desenvolvidas e integradas em data centers, redes e plataformas de computação embarcadas.

Conclusão

O EPM7128ATC100-10 é um dispositivo lógico programável projetado para lidar com tarefas de controle digital configuráveis em sistemas eletrônicos.Ele combina 128 macrocélulas e uma estrutura de roteamento interno que permite construir funções lógicas personalizadas dentro de um chip compacto.O dispositivo organiza seus recursos lógicos por meio de blocos de matriz lógica que se conectam por meio de uma rede de roteamento programável.Sua configuração de pinos e pacote TQFP compacto suportam designs de montagem em superfície usados em placas de circuito modernas.Você pode usar este dispositivo para gerenciar roteamento de sinal, sequenciamento lógico e funções de controle em muitas aplicações digitais.Essa flexibilidade ajuda a simplificar o projeto do circuito, ao mesmo tempo que mantém o comportamento do sistema previsível.

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

perguntas frequentes [FAQ]

1. Que tipo de dispositivo é o EPM7128ATC100-10?

EPM7128ATC100-10 é um dispositivo lógico programável complexo que permite lógica digital configurável para ser implementada dentro de um único sistema integrado circuito.

2. Quantas macrocélulas estão disponíveis no EPM7128ATC100-10?

O dispositivo contém 128 macrocélulas que podem implementar funções lógicas combinacionais ou registradas programáveis.

3. Qual pacote o EPM7128ATC100-10 usa?

Ele está disponível em um pacote quádruplo fino de 100 pinos que suporta instalação de montagem em superfície em placas de circuito impresso.

4. Quais são os usos comuns do EPM7128ATC100-10?

É comumente usado para lógica de controle digital, roteamento de sinal, gerenciamento de interface e implementação de máquina de estado em sistemas embarcados sistemas.

5. Qual tensão de alimentação o EPM7128ATC100-10 requer?

O dispositivo opera com uma faixa de tensão de alimentação interna de aproximadamente 3 volts a 3,6 volts.

Dentro do dispositivo de armazenamento flash NOR S29GL256N11FFI020

em 13/03/2026

O que o FPGA EPF8282AVTC100-4 faz em sistemas digitais

em 10/03/2026

Postagens populares

-

Computadores de conjunto de instruções complexos: como eles mudaram de computação?

em 19/04/8000 147782

-

Pinagem e recursos USB-C

em 19/04/2000 112070

-

Usando o Xilinx Unified Simulation Primitives: um guia abrangente para design e simulação do FPGA

em 19/04/1600 111352

-

Tensões de fonte de alimentação em eletrônica: significado de VCC, VDD, VEE, VSS e GND

em 19/04/0400 83828

-

Guia do conector RJ45: pinagem, fiação, tipos de cabos e usos

em 01/01/1970 79641

-

O guia final para os códigos de cores de arame em sistemas elétricos modernos

A maneira como nossos sistemas elétricos usam cores não é apenas para a aparência.Cada cor do fio agora indica uma função específica, facilitando a identificação e manuseio componentes elétricos co...em 01/01/1970 67006

-

Guia da válvula de purga: função, sintomas, teste e substituição para o desempenho ideal do motor

A válvula de purga é uma parte essencial do sistema de um carro que ajuda a manter o ar limpo, gerenciando vapores de combustível antes que eles possam escapar da atmosfera.Isso não apenas ajuda o ...em 01/01/1970 63131

-

Fator de qualidade (Q): equações e aplicações

O fator de qualidade, ou 'q', é importante ao verificar como os indutores e ressonadores trabalham em sistemas eletrônicos que usam frequências de rádio (RF).'Q' mede o quão bem um circuito minimiz...em 01/01/1970 63067

-

Alcançando o desempenho máximo com o teorema máximo de transferência de energia

O teorema da transferência de energia máxima explica como a energia de uma fonte, como uma bateria ou gerador, flui para uma carga conectada.Ele mostra a condição exata em que a carga recebe mais e...em 01/01/1970 54097

-

A23 Especificações da bateria e compatibilidade

A bateria A23 é uma pequena bateria em forma de cilindro com alta tensão.Também chamado 23A, 23AE, ou MN21, funciona a 12 volts e muito mais alto que as baterias AA ou AAA.Seu design espec...em 01/01/1970 52224