Compreendendo a arquitetura e aplicações do FPGA XC2S200-5FG256I

Você pode estar procurando um dispositivo lógico programável que permita moldar o hardware digital exatamente da maneira que seu sistema precisa.O FPGA XC2S200-5FG256I oferece blocos lógicos flexíveis, memória interna e muitas conexões de entrada e saída para que você possa criar funções digitais personalizadas dentro de um dispositivo.Sua arquitetura suporta roteamento de sinal, controle de tempo e manipulação de interface em muitos tipos de equipamentos eletrônicos.Com roteamento programável e recursos de memória disponíveis no chip, você pode adaptá-lo a diferentes tarefas de controle, caminhos de comunicação e funções de sistema embarcado sem alterar o hardware físico.Catálogo

Visão geral do XC2S200-5FG256I

O XC2S200-5FG256I é um dispositivo lógico programável construído na arquitetura FPGA Spartan II e projetado para sistemas digitais configuráveis.Ele fornece cerca de 200.000 portas lógicas organizadas por meio de blocos lógicos configuráveis que podem ser programados para implementar funções digitais personalizadas.O bloco RAM integrado suporta armazenamento temporário de dados, enquanto um grande número de pinos de entrada e saída permite comunicação flexível com componentes externos.O dispositivo opera a partir de uma fonte central de baixa tensão e suporta condições de temperatura industrial.Sua arquitetura suporta prototipagem de hardware, controle de interface e tarefas de processamento digital em equipamentos eletrônicos embarcados.

Procurando por XC2S200-5FG256I?Entre em contato conosco para verificar o estoque atual, prazo de entrega e preços.

XC2S200-5FG256Ib

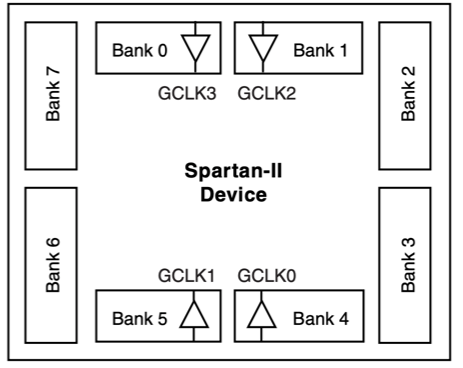

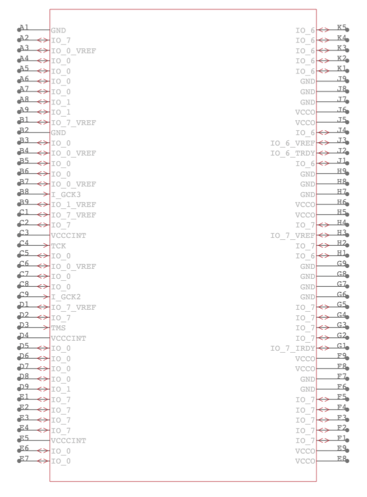

A estrutura de E/S divide o perímetro do dispositivo em oito bancos posicionados ao longo de todos os quatro lados do pacote FPGA.Cada banco agrupa um conjunto de pinos de entrada e saída que compartilham a mesma alimentação VCCO, permitindo que um nível de tensão consistente seja aplicado a todos os pinos daquela região.As entradas de relógio global rotuladas de GCLK0 a GCLK3 são colocadas próximas às seções inferior e superior do layout para distribuir os sinais de relógio uniformemente pela matriz lógica interna.Este arranjo permite que vários padrões de sinalização operem simultaneamente, atribuindo diferentes níveis de tensão a bancos separados, enquanto mantém o roteamento organizado entre os pinos externos e a lógica programável interna.

Modelo CAD XC2S200-5FG256I

Símbolo XC2S200-5FG256I

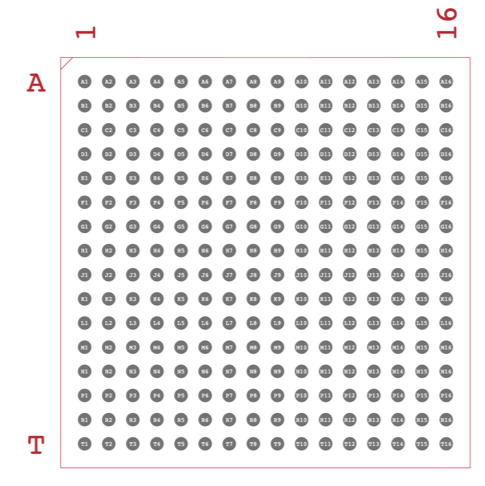

Pegada XC2S200-5FG256I

XC2S200-5FG256I Modelo 3D

Recursos do XC2S200-5FG256I

Arquitetura lógica FPGA programável

O dispositivo utiliza uma estrutura lógica configurável que permite que circuitos digitais sejam definidos através de blocos lógicos programáveis e caminhos de roteamento.Essa estrutura permite que os projetistas implementem comportamento de hardware personalizado sem modificar o dispositivo físico, apoiando o desenvolvimento flexível de sistemas digitais e a prototipagem de hardware.

Recursos de memória de bloco integrados

O bloco interno RAM fornece armazenamento de memória dedicado dentro da malha programável.Esses blocos de memória suportam buffer de dados, tabelas de consulta e operações de armazenamento temporário, reduzindo a necessidade de componentes de memória externos em muitas aplicações de processamento digital.

Interface de entrada e saída configurável

Até 176 pinos de entrada e saída do usuário fornecem conectividade flexível com dispositivos externos.Cada pino pode ser configurado para diferentes funções de entrada, saída ou bidirecionais, permitindo que o dispositivo interaja com sensores, interfaces de comunicação e sistemas de controle.

Rede de roteamento programável

Uma rede de interconexão programável conecta blocos lógicos, elementos de memória e interfaces de entrada e saída.Os sinais podem ser roteados através de caminhos configuráveis, permitindo fluxo de sinal personalizado entre recursos internos, mantendo ao mesmo tempo um comportamento digital previsível.

Gerenciamento de relógio usando loops bloqueados por atraso

Circuitos integrados de loop bloqueado com atraso suportam distribuição de relógio e alinhamento de tempo dentro do dispositivo.Esses circuitos ajudam a manter relações de temporização estáveis entre seções lógicas internas e fontes de relógio externas.

Capacidade operacional em temperatura industrial

O dispositivo suporta operação em uma ampla faixa de temperatura adequada para ambientes industriais.Isto permite um desempenho estável em sistemas expostos a condições ambientais variadas, como equipamentos de fábrica ou instalações externas.

Pacote BGA compacto para montagem em superfície

O dispositivo é embalado em um formato de grade de 256 bolas que permite um grande número de conexões em um espaço compacto.Este estilo de embalagem suporta layouts densos de placas de circuito impresso, mantendo a confiabilidade elétrica para dispositivos com alta contagem de pinos.

Especificações Técnicas XC2S200-5FG256I

| Atributo do produto | Valor do Atributo |

| Fabricante | AMD Xilinx |

| Tensão - Alimentação | 2,375 V ~ 2,625 V |

| Total de bits de RAM | 57344 |

| Pacote de dispositivos do fornecedor | 256-FBGA (17x17) |

| Série | Spartan®-II |

| Pacote/Caixa | 256-BGA |

| Pacote | Bandeja |

| Temperatura operacional | -40°C ~ 100°C (TJ) |

| Número de elementos/células lógicas | 5292 |

| Número de LABs/CLBs | 1176 |

| Número de E/S | 176 |

| Número de portões | 200.000 |

| Tipo de montagem | Montagem em superfície |

| Número básico do produto | XC2S200 |

| Status RoHS | RoHS não compatível |

| Nível de sensibilidade à umidade (MSL) | 3 (168 horas) |

| Estado do REACH | REACH não afetado |

| ECCN | EAR99 |

| HTSU | 8542.39.0001 |

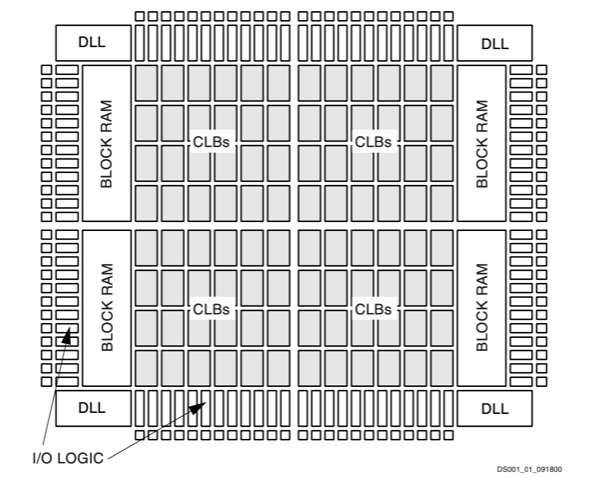

Diagrama de blocos de XC2S200-5FG256I

A grade central de blocos lógicos configuráveis forma a estrutura lógica programável onde as funções digitais são implementadas usando tabelas de consulta e flip-flops.Colunas verticais rotuladas como bloco RAM fornecem recursos de memória incorporados colocados ao lado da matriz lógica para armazenamento de dados e operações de buffer.Os blocos lógicos de entrada e saída alinham as bordas externas do dispositivo e conectam a rede de roteamento interna aos pinos externos.As unidades de loop bloqueado por atraso localizadas nos cantos suportam o alinhamento do relógio e o controle de tempo em toda a estrutura lógica interna.Os caminhos de interconexão entre o array CLB, colunas de memória, unidades de clock e blocos de E/S criam a rede de roteamento programável que permite conexões de sinal flexíveis em todo o dispositivo.

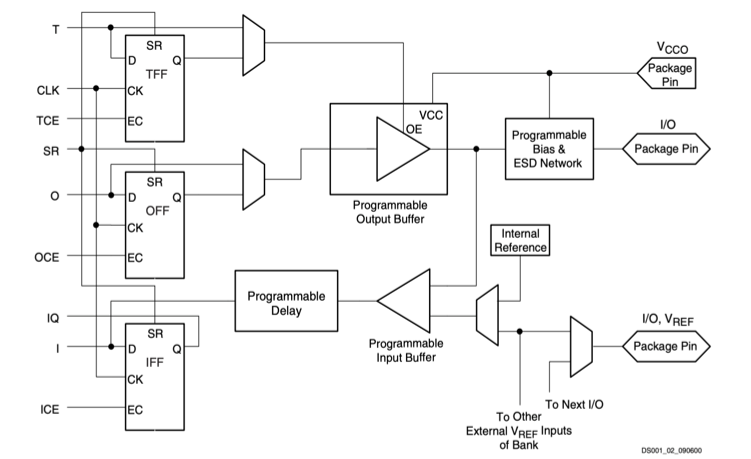

Bloco de entrada/saída (IOB) de XC2S200-5FG256I

A estrutura interna do bloco de E/S conecta os pinos do pacote externo à malha lógica programável por meio de caminhos de entrada e saída configuráveis.Os dados de saída passam por um flip-flop rotulado como OFF com controle de clock e habilitação, seguido por um buffer de saída programável que aciona o pino externo enquanto opera a partir da fonte VCCO associada ao banco de E/S.Os sinais de entrada do pino do pacote entram através de um buffer de entrada programável e um estágio de atraso programável opcional antes de chegar a um flip-flop de entrada denominado IFF que sincroniza o sinal com o relógio interno.Elementos de controle adicionais incluem controle de estado triplo através do registro TFF, sinais de habilitação de clock e entradas de reinicialização definidas que gerenciam a temporização do sinal e o controle de estado.Uma rede de proteção contra ESD e polarização programável protege a interface de pinos, enquanto uma referência interna e conexões VREF suportam padrões de E/S referenciados por tensão compartilhados por todo o banco.

Aplicações de XC2S200-5FG256I

Sistemas de roteamento de sinais digitais

Recursos lógicos programáveis permitem que o dispositivo gerencie o roteamento e processamento de sinais digitais em equipamentos de comunicação.Seus blocos lógicos configuráveis podem implementar caminhos lógicos personalizados que controlam a transferência de dados entre componentes do sistema, mantendo um comportamento de temporização estável.

Unidades de controle de automação industrial

Os sistemas de controle industrial geralmente exigem uma lógica digital flexível que possa se adaptar a diferentes processos de máquinas.O dispositivo pode gerenciar sinais de controle, entradas de sensores e saídas de atuadores, suportando uma operação confiável em ambientes de produção automatizados.

Plataformas de prototipagem de hardware embarcadas

As plataformas de desenvolvimento frequentemente usam dispositivos lógicos programáveis para testar projetos digitais antes da produção final do hardware.O dispositivo permite que os projetistas implementem e modifiquem estruturas lógicas durante o desenvolvimento, permitindo testes eficientes de funções de controle digital.

Ponte de interface de comunicação

Os sistemas que conectam vários protocolos de comunicação podem usar o dispositivo para traduzir ou rotear sinais digitais entre interfaces.Sua lógica programável permite caminhos de dados personalizados que vinculam processadores, dispositivos de memória e controladores de comunicação.

Subsistemas Eletrônicos Automotivos

Unidades de controle eletrônico em veículos requerem lógica programável para gerenciamento de sinais e coordenação de sistemas.O dispositivo pode lidar com tarefas de controle digital, interfaces de comunicação e funções de temporização em eletrônicos automotivos.

Lógica de controle eletrônico de consumo

Os dispositivos digitais de consumo geralmente exigem lógica programável compacta para gerenciar as funções do sistema.O dispositivo pode coordenar sinais de interface do usuário, controle de tempo e comunicação interna entre componentes de produtos eletrônicos.

Vantagens e desvantagens do XC2S200-5FG256I

Vantagens

• Estrutura lógica programável permite que circuitos digitais sejam reconfigurados após a instalação

• A memória de bloco integrada suporta armazenamento de dados sem memória externa em alguns designs

• Grande número de pinos de entrada e saída suporta conectividade de sistema flexível

• Operação estável em condições de temperatura industrial

• O pacote BGA compacto suporta layouts densos de placas de circuito impresso

• Circuitos internos de alinhamento de relógio ajudam a manter um comportamento de temporização consistente

Desvantagens

• A capacidade lógica é inferior à dos dispositivos programáveis mais recentes

• O tamanho da memória no chip é limitado em comparação com famílias modernas de lógica programável

• O consumo de energia pode ser maior do que as arquiteturas de baixa tensão mais recentes

• Não inclui recursos avançados de processamento de sinal integrado

• Requer memória de configuração externa para programação do dispositivo

Alternativas XC2S200-5FG256I

| Número da peça | Fabricante | Principais recursos | Caso de uso/Notas |

| XC2S200-5FGG256I | AMD | FPGA Spartan-II com blocos lógicos configuráveis, RAM distribuída e recursos de roteamento programáveis.Ele opera em torno de uma fonte central de 2,5 V e fornece milhares de células lógicas para implementação de circuitos digitais personalizados. | Usado em processamento embarcado, controle industrial e hardware de comunicação onde lógica programável e operação confiável em faixas de temperatura industrial são necessárias. |

| XC2S200-5FGG256C | AMD | Dispositivo FPGA da família Spartan-II que integra elementos lógicos programáveis, blocos de memória interna e conexões de E/S configuráveis para design digital flexível. | Adequado para produtos eletrônicos de consumo, módulos de comunicação e plataformas de prototipagem onde são necessárias densidade lógica moderada e configuração de hardware flexível. |

| XC2S200-5FG256C | AMD | Dispositivo FPGA programável que oferece células lógicas configuráveis, recursos de memória interna e vários pinos de E/S configuráveis pelo usuário para implementar circuitos digitais complexos em um único chip. | Aplicado em sistemas de aquisição de dados, plataformas de processamento de sinais e projetos embarcados que necessitam de hardware digital programável. |

| XC2S200-5FGG456I | AMD | FPGA Spartan-II de alta contagem de pinos que fornece blocos lógicos programáveis, memória incorporada e um grande número de conexões de E/S para sistemas digitais complexos. | Usado em automação industrial, equipamentos de comunicação avançados e sistemas embarcados de alta E/S que exigem lógica programável flexível e suporte estendido de temperatura. |

Sobre AMD Xilinx

AMD Xilinx é uma empresa de tecnologia de semicondutores conhecida pelo desenvolvimento de dispositivos lógicos programáveis e plataformas de computação adaptativas.A empresa originou-se como Xilinx e mais tarde tornou-se parte da Advanced Micro Devices.Seu trabalho se concentra em matrizes de portas programáveis em campo, sistemas adaptativos em dispositivos de chip e plataformas de aceleração programáveis usadas em computação, comunicações, eletrônica automotiva e sistemas industriais.A empresa desenvolve arquiteturas lógicas programáveis há várias décadas, apoiando projetos de hardware digital por meio de dispositivos configuráveis que permitem que os circuitos sejam definidos após a fabricação.Seus produtos são amplamente utilizados em sistemas embarcados, infraestrutura de rede, equipamentos de processamento de sinais e sistemas de controle eletrônico.

Conclusão

O FPGA XC2S200-5FG256I oferece uma maneira flexível de construir lógica digital diretamente no hardware.Você pode configurar seus blocos lógicos, recursos de memória e conexões de entrada e saída para suportar diferentes tarefas do sistema.Sua estrutura interna permite roteamento de sinal, controle de tempo e armazenamento de dados dentro de um único dispositivo programável.Com sua arquitetura configurável de arquitetura e aplicativos FPGA XC2S200-5FG256I, o dispositivo pode suportar eletrônicos embarcados, interfaces de comunicação e sistemas de controle.Compreender seu layout, recursos e aplicações ajuda você a ver como os dispositivos lógicos programáveis suportam equipamentos digitais modernos.Isso torna mais fácil avaliar se o XC2S200-5FG256I atende às necessidades do seu projeto eletrônico.

Folha de dados PDF

Folha de dados XC2S200-5FG256I:

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

perguntas frequentes [FAQ]

1. Que tipo de dispositivo é XC2S200-5FG256I

XC2S200-5FG256I é um array de portas programável em campo.É um dispositivo lógico programável que permite configurar circuitos digitais através de software em vez de design de hardware fixo.

2. Quantos pinos de entrada e saída o XC2S200-5FG256I fornece

O dispositivo XC2S200-5FG256I suporta até 176 entradas configuráveis pelo usuário e pinos de saída, permitindo a conexão com muitos componentes externos e interfaces de comunicação.

3. Qual é a finalidade do bloco de RAM no FPGA XC2S200

Block RAM fornece memória interna usada para armazenamento temporário de dados, buffer, tabelas de pesquisa e outras tarefas de manipulação de dados dentro do sistema lógico programável.

4. Onde o XC2S200-5FG256I é comumente usado

Este dispositivo é frequentemente usado em eletrônica embarcada, comunicação sistemas, equipamentos de automação industrial e sistemas de controle digital que requerem lógica de hardware programável.

5. Que tipo de pacote o XC2S200-5FG256I usa

O XC2S200-5FG256I é embalado em um formato de grade de 256 bolas, que permite um grande número de conexões em um espaço compacto adequado para layouts densos de placas de circuito.

Compreendendo os conectores DVI: tudo o que você precisa saber

em 09/03/2026

Guia, recursos e aplicações do chip de interface ADM560JRS

em 05/03/2026

Postagens populares

-

Computadores de conjunto de instruções complexos: como eles mudaram de computação?

em 18/04/8000 147758

-

Pinagem e recursos USB-C

em 18/04/2000 111960

-

Usando o Xilinx Unified Simulation Primitives: um guia abrangente para design e simulação do FPGA

em 18/04/1600 111351

-

Tensões de fonte de alimentação em eletrônica: significado de VCC, VDD, VEE, VSS e GND

em 18/04/0400 83726

-

Guia do conector RJ45: pinagem, fiação, tipos de cabos e usos

em 01/01/1970 79512

-

O guia final para os códigos de cores de arame em sistemas elétricos modernos

A maneira como nossos sistemas elétricos usam cores não é apenas para a aparência.Cada cor do fio agora indica uma função específica, facilitando a identificação e manuseio componentes elétricos co...em 01/01/1970 66930

-

Guia da válvula de purga: função, sintomas, teste e substituição para o desempenho ideal do motor

A válvula de purga é uma parte essencial do sistema de um carro que ajuda a manter o ar limpo, gerenciando vapores de combustível antes que eles possam escapar da atmosfera.Isso não apenas ajuda o ...em 01/01/1970 63078

-

Fator de qualidade (Q): equações e aplicações

O fator de qualidade, ou 'q', é importante ao verificar como os indutores e ressonadores trabalham em sistemas eletrônicos que usam frequências de rádio (RF).'Q' mede o quão bem um circuito minimiz...em 01/01/1970 63019

-

Alcançando o desempenho máximo com o teorema máximo de transferência de energia

O teorema da transferência de energia máxima explica como a energia de uma fonte, como uma bateria ou gerador, flui para uma carga conectada.Ele mostra a condição exata em que a carga recebe mais e...em 01/01/1970 54086

-

A23 Especificações da bateria e compatibilidade

A bateria A23 é uma pequena bateria em forma de cilindro com alta tensão.Também chamado 23A, 23AE, ou MN21, funciona a 12 volts e muito mais alto que as baterias AA ou AAA.Seu design espec...em 01/01/1970 52160